RapidIO与DDR在电子技术领域扮演着关键角色。RapidIO是一种高性能、低引脚数的基于数据包交换的互连技术,而DDR则是内存技术的代表。它们在众多硬件系统中发挥着至关重要的作用。同时,这两者之间存在着一些值得深入研究的连接与交互模式。

RapidIO概述

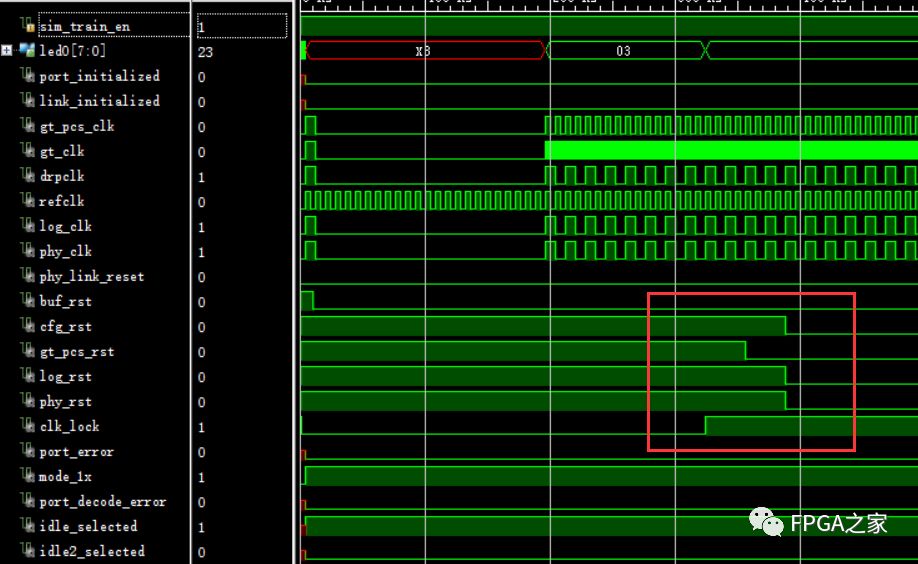

RapidIO技术主要用于嵌入式系统。这项技术为处理器、FPGA等组件提供了高速通信的途径。在具体应用中,比如在高端服务器上,RapidIO能够确保不同芯片间的数据快速交换。它具有高速率、低延迟等特点。每个RapidIO端口都能设置为特定的工作模式,以适应不同的硬件环境。因此,在处理复杂的多芯片系统通信时,RapidIO表现出色。

RapidIO的协议极为灵活,能够根据用户的具体需求进行定制化配置。这包括对数据包尺寸和路由算法等方面的调整。这样的特性极大地便利了工程师们在系统设计过程中的工作,并有助于有效提升系统的整体性能。

DDR技术剖析

DDR内存,又称双倍数据率同步动态随机存取存储器。这种内存能在时钟的上升沿和下降沿同时传输数据,显著提升了数据传输的带宽。在我们的日常使用中,电脑的DDR内存性能对整体运行速度有着显著影响。

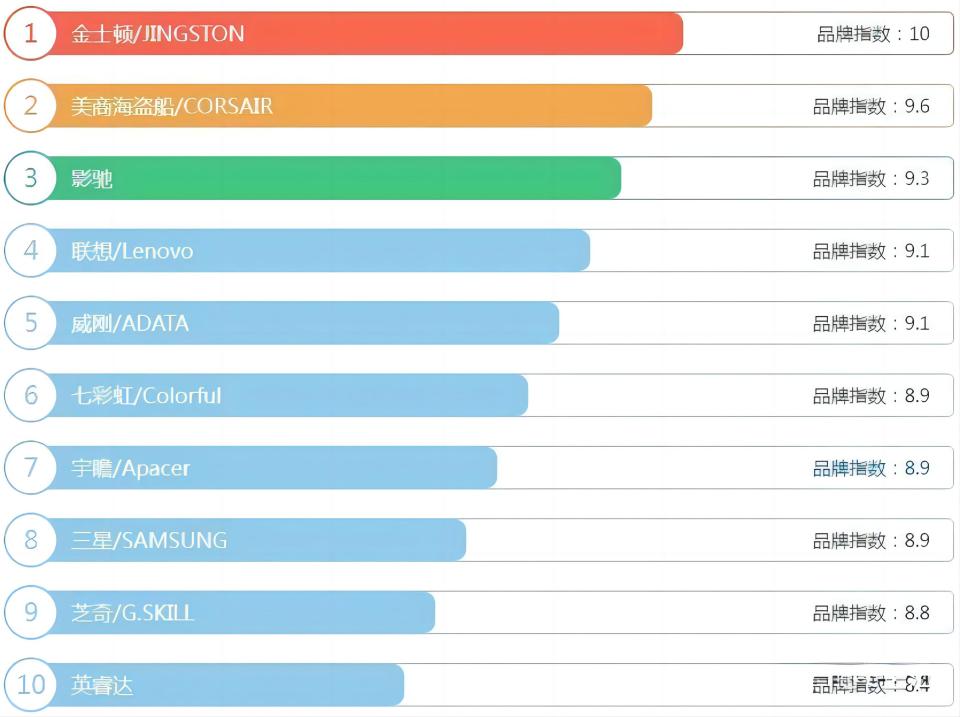

DDR的规格持续升级,从DDR1到DDR5,每一代都提升了频率,降低了功耗。同时,DDR的兼容性极强,能在多种主板和平台上顺畅运行。然而,DDR也有其局限,例如在高频工作时可能会遇到信号完整性的难题,这需要采取相应的优化手段来克服。

RapidIO与DDR的交互需求

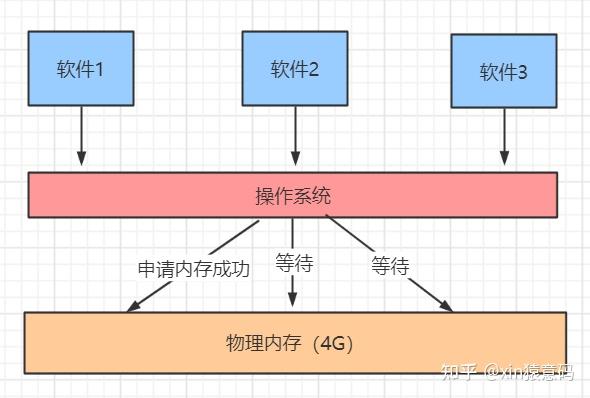

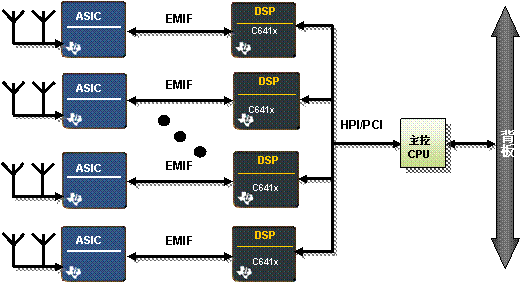

在一个复杂的系统中,RapidIO与DDR的交互是必不可少的。比如,在通信基站中,处理器必须借助RapidIO与芯片实现快速通讯。同时,它还得频繁地读写DDR内存,以存储和获取数据。若这两者间的交互出现障碍,整个系统的性能便会遭遇瓶颈。

在硬件设计上,我们必须制定出合理的通信方案,以保证RapidIO与DDR间的数据传输能够高效进行。此外,还需注意它们之间的时间同步,以防止出现数据冲突等问题。

数据传输链路的构建

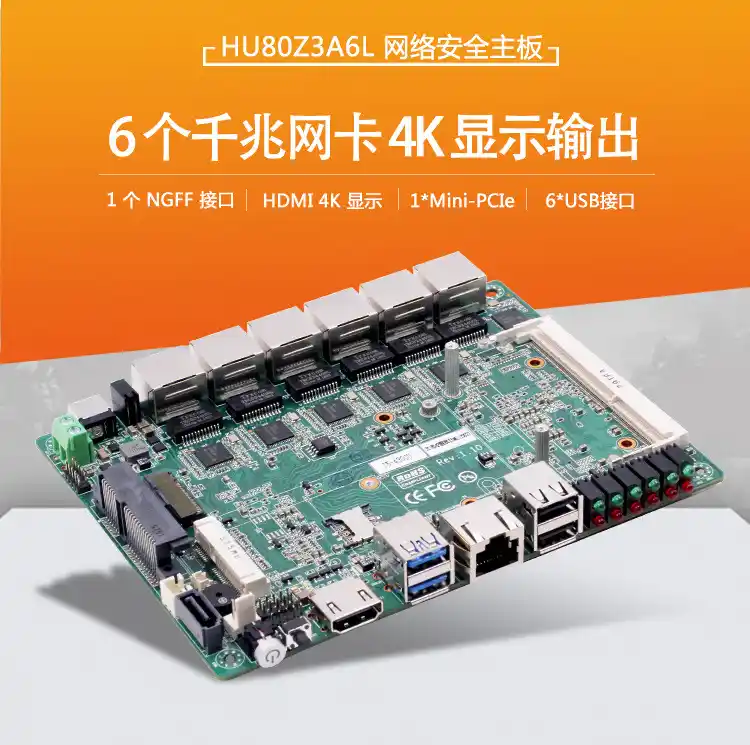

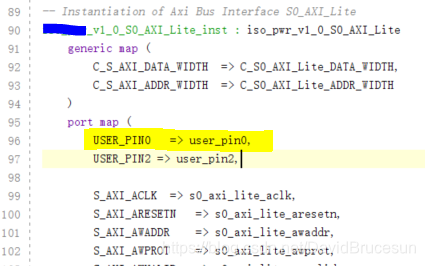

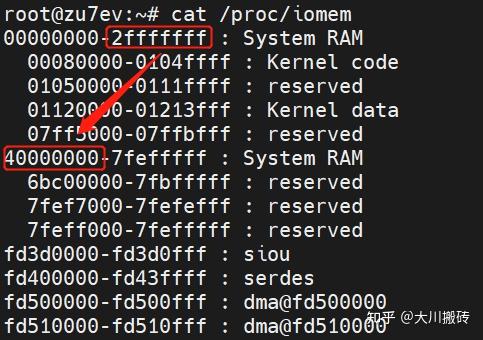

建立RapidIO与DDR之间的数据传输链路并非易事。首先,硬件连接是关键,需挑选合适的接口类型和电平标准。在特定工业环境下,还可能需要采用特殊芯片,以确保信号质量和传输距离。

从逻辑上讲,编写恰当的驱动程序与控制逻辑是关键。这要求对RapidIO协议及DDR的操作时序有深刻理解。只有做到这一点,才能确保数据在RapidIO与DDR之间传输的可靠性。

性能优化方面

为了提升RapidIO与DDR间的交互效率,我们可实施多种优化手段。首先,在设计电路时,选用更优质的布线材料,并合理规划线路布局,以此减少信号干扰。其次,在软件层面,我们可以调整内存访问方式以及缓存策略等。

以智能交通系统的数据处理模块为例,优化RapidIO与DDR的性能,能加速处理传感器传来的数据。这样,系统对交通状况的反应速度得以提高。若不这么做,数据可能会堆积,处理也会延迟,进而影响交通管理的效率。

未来发展趋势

科技不断进步,RapidIO与DDR技术亦同步发展。展望未来,我们有望目睹速度更快的RapidIO接口和性能更强的DDR内存问世。此外,两者间的集成度有望进一步提升,或许将诞生专为它们交互优化的新型芯片或技术架构。

同时,针对人工智能和大数据分析等新兴应用场景,RapidIO与DDR如何调整特性以更好地满足需求,这无疑是一个备受关注的发展趋势。

在此,我想请教大家,在你们的工作实践或是兴趣学习过程中,是否遇到过与RapidIO和DDR相关联的技术难题?欢迎在评论区留下你们的经验,同时,也期待大家的点赞和这篇文章的转发。