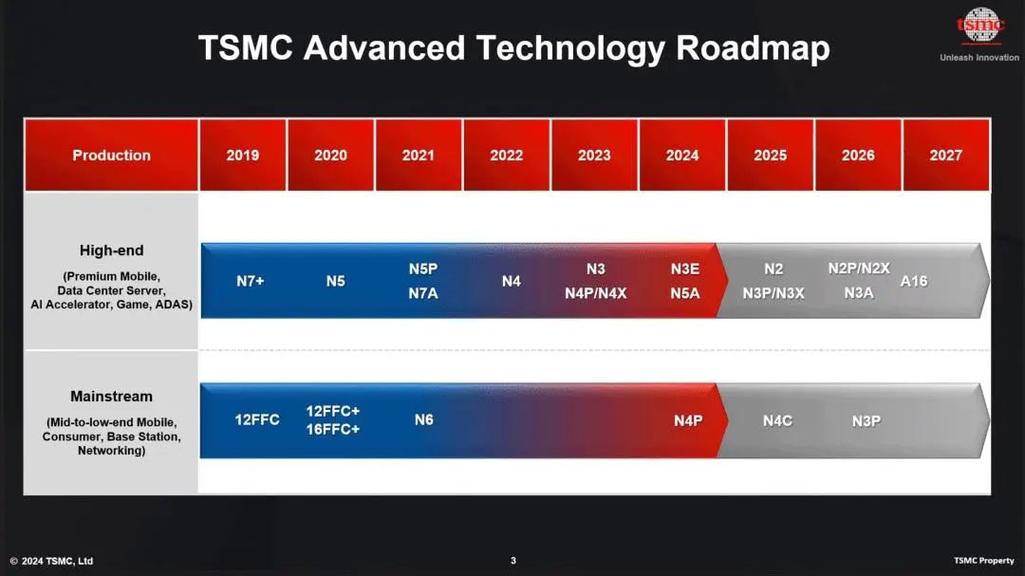

当前科技迅猛进步,台积电于12月15日的IEDM2024会议上公布了2nm工艺技术的新动态,这一信息迅速引起了广泛关注。这一突破预示着芯片制造技术即将发生显著变化,晶体管密度和性能指标都将实现显著提升。

晶体管密度和性能功耗的提升

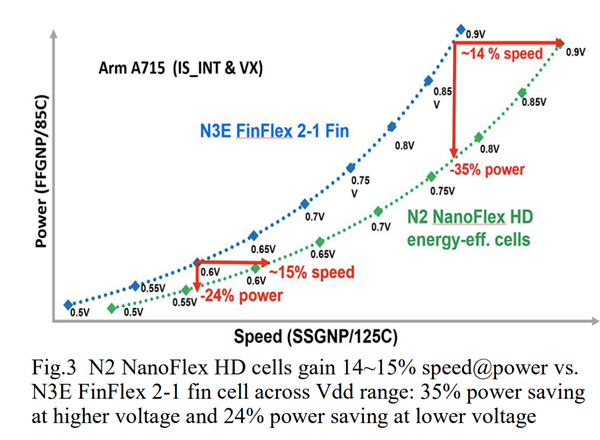

2024年12月15日,于IEDM2024会议上,台积电展出的2纳米制程技术,相较于3纳米制程,晶体管密度提升了15%。这一提升使得在相同面积内可容纳更多晶体管,从而显著促进了芯片性能的增强。此外,在相同功耗条件下,性能可提升至15%,而在保持同等性能的前提下,功耗则可降低24至35%。这些数据充分揭示了2纳米制程在能效管理方面的卓越成就。

终端设备将面临重大变革。若手机处理器采用2nm制程技术,即便电池续航保持不变,其性能将显著提升;反之,若性能维持原状,续航时间则可显著增加,从而满足用户对高能效和长使用时间的双重要求。

全环绕栅极晶体管的引入

台积电推出了2nm工艺节点的全环绕栅极(GAA)纳米片晶体管。该晶体管能够调节通道宽度,从而为性能与能效的均衡提供了新的技术途径。在现代芯片设计中,性能与能效的协调至关重要。

在服务器芯片设计中,既要确保处理大量数据时的卓越性能,也要注重能效以减少运营成本。GAA纳米片晶体管技术允许芯片设计者根据实际需求,更有效地平衡性能和能效,从而为芯片的个性化设计提供了更多选择。

NanoFlexDTCO发挥作用

NanoFlexDTCO(设计技术联合优化)这一新工艺具备独特优势。它能创造出两种不同类型的单元:一类是面积最小化且能效提升的较矮单元;另一类则是性能最大化且较高的单元。

优化设计在各类芯片产品中扮演着不同角色。在移动芯片领域,最小化面积有助于缩小芯片体积,同时提升能效,增强设备续航能力。至于高性能计算芯片,最大化性能能够加快数据处理速度,更好地满足复杂运算需求。

第三代偶极子集成

2纳米制程技术融合了第三代偶极子集成技术,涵盖N型和P型,这实现了六个电压阈值档(6-Vt)的支持,其电压范围达到200毫伏。此技术显著提升了芯片电压调节的精确度。

芯片运行期间,精确的电压控制极为关键。通过不同的电压级别,芯片能够在不同工作模式下更高效地分配电力资源。以智能手表中的芯片为例,它能够根据不同的应用需求,如待机、日常步数统计、健康数据监测等,调整至适宜的电压级别,以此实现电量的节约。

纳米片晶体管的速度和能效提升

经过多方面优化,N型和P型纳米片晶体管的电流-电压响应速度分别提高了70%和110%。在0.5至0.6伏特低电压条件下,新型纳米片晶体管展现出显著的能效增长,其频率提高了约20%,同时待机功耗减少了约75%。与传统的FinFET晶体管相比,新技术的纳米片晶体管表现出更优的性能。

物联网传感器节点等对能耗要求较高的设备,若能减少待机状态下的功耗,将显著增加其运行时间。同时,对于追求高性能的设备,例如游戏机,提高运行频率将有助于提升游戏体验的流畅度。

其他新工艺优势

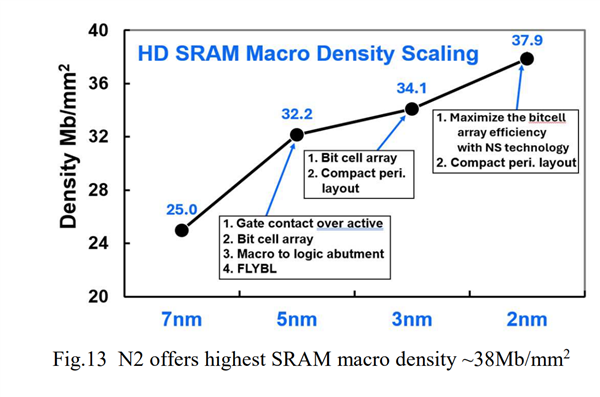

2nm工艺的SRAM芯片密度创下了新高,每平方毫米可容纳约38Mb。此外,采用了创新的MOL中段和BEOL后段工艺,电阻减少了20%,能效得到显著提升。第一层金属层(M1)的生产流程简化,只需一步蚀刻和一次EVU曝光即可完成,显著减少了复杂度和光罩需求。同时,针对高性能计算,引入了超高性能的SHP-MiM电容,每平方毫米容量约200fF,支持更高的运行频率。这些新技术的应用共同推动了芯片整体性能的提升。

在人工智能芯片的生产过程中,提升静态随机存取存储器(SRAM)的密度有助于提升数据存储与读取的效率。同时,减少电阻值和简化制造流程能够有效减少成本,并提升产品合格率。

台积电的2纳米制程技术实现了多项关键突破。在当前全球芯片市场竞争日趋激烈的背景下,这一技术成就对芯片产业格局可能带来何种影响?诚挚邀请读者在评论区发表见解,并对本文给予点赞及转发。