身为一位硬件工程师,我具备深入研究DDR4内存时序设计之才能。内存时序即为在内存模块执行读取与写入任务时,各信号间的时间关联及顺序安排。通过精准的时序规划及关键性优化措施,能够提升内存效率及运行稳定度,进而满足计算机系统对内存带宽及反应速率的严格要求。

什么是DDR4内存时序?

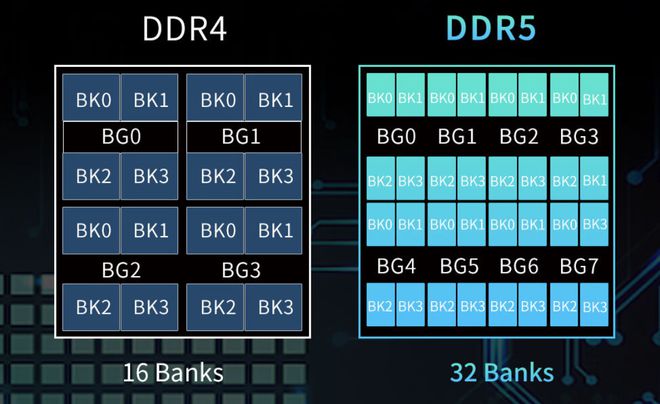

DDR4内存时序包含诸多参数如CL、tRCD、tRP与tRAS等,以确保内存运行效率。其中,CL即代表从列地址编译至数据读取所需的延迟周期数;同样,tRCD指称行地址编译至列地址编译期间的等待周期。这些参数的精准设定关乎着内存运行速度及稳定性。

DDR4内存的严格时序参数设定需结合多项因素,涵盖工作频率、电压与温度等方面。精确调节这些因素可使内存模组在各个运行环境下持续保持卓越的稳定性。因此,在实践操作中,必须针对特定需求细致地调整DDR4内存。

DDR4内存时序参数有哪些影响?

硬件优化:适当调整时序电路参数可有效提升内存模块读写效能。降低 CL 值有助于提速显着的内存读取效率,而适当地调整 tRCD,tRP 等参数亦有助于提升内存写入性能。

稳定度优势:适当调整时序参数有助于提升内存模块的稳定性。不当的参数值会引发读写失效或系统崩溃等问题,需要合理权衡。

能耗:时序设计对内存模块的能效有直接影响。宽松的设定可能会引发额外的电能消耗;而过短控制设计则易产生信号紊乱及运行不稳定的问题。

如何进行DDR4内存时序优化?

参照厂商推荐:先详尽掌握DDR4内存模组厂商对时序特性所提供的调整建议,以此作为最佳实践的开端。

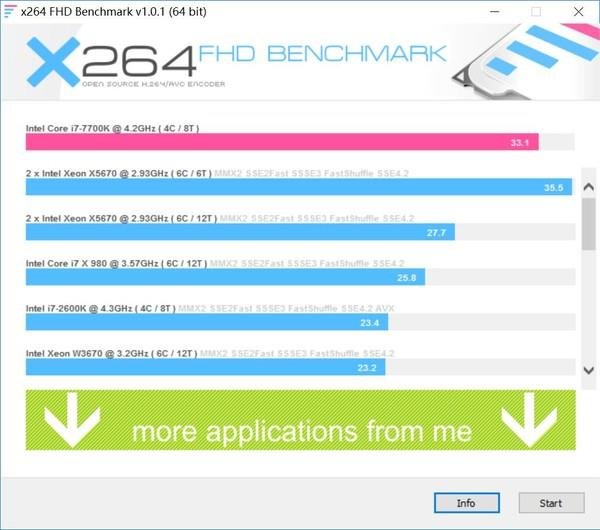

系统测试:运用专业测试软件与仪器,针对各式时序排列进行精密检测;依据测试成果,为量身制定最优参数设定。

阶梯式调整:建议逐级微调各个时间序列参数,多次尝试把握最优组合,同时需兼顾各参数间的协同均衡。

散热考虑:过于紧张的时序可能导致内存模组升温,故优化过程中务必关注散热因素,以维持系统稳定性。

DDR4内存时序与超频

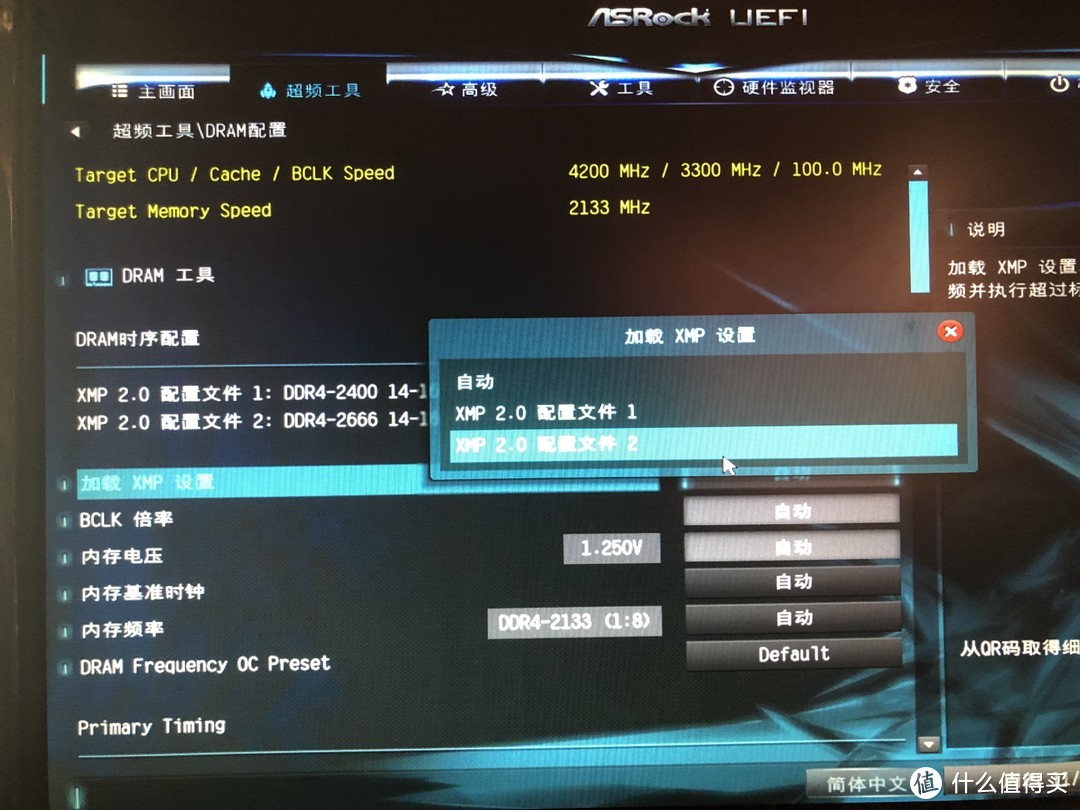

超频技术提升硬件性能的核心在于调整频率。在此过程中,尤其关键的是合理设定DDR4内存模块的时序参数。以精细调节这些参数,方可成就更稳定的超频效果和最大化挖掘硬件潜能。

在超频实践中,可不仅限于提升主频,还包括通过调整DRAM电压及修改CL值来达到高性能表现。虽然如此,实施超频仍需谨慎,因为不当的时序配置可能引发系统稳定性问题,严重者甚至会损害硬件设备。

结论

总括而言,DDR4内存时序设计对计算机系统性能显得至关重要。通过精确设定各参数及有效优化,能提升内存模块的数据传输速度与可靠性,且有利于降低能耗。而在超频等特殊情况下,也要注重时序设定,以免影响系统整体稳定性。

期望此文能助您深入了解DDR4内存时序知识。敬请分享宝贵见解,探讨DDR4内存时序的设计及优化技巧!