身为电子工程专家,理解并掌握DDR SDRAM时序对系统设计与性能优化具有举足轻重的影响力。那么,何为DDR SDRAM时序?其主要涵盖了哪些方面?以及应如何准确把握并有效运用这些时序规则?请随笔者共同深入探索这一主题。

什么是DDR SDRAM?

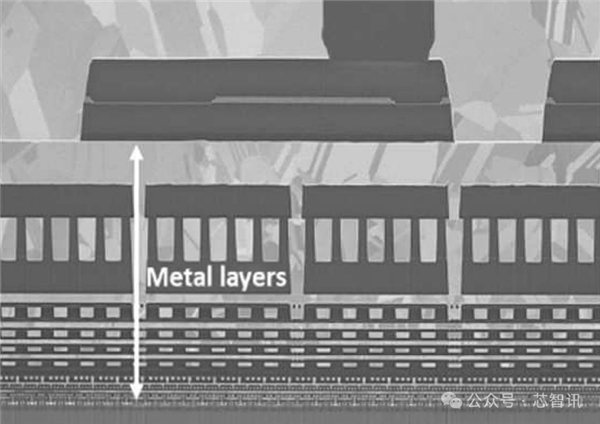

首先,让我们掌握DDR SDRAM的基础知识。阐述如下:SDRAM,全称为同步动态随机存取存储器(Synchronous Dynamic Random Access Memory),这一类存储器被广泛应用于计算机内部。而DDR SDRAM,即双倍数据率同步动态随机存取存储器的缩写,虽然与传统SDRAM同样以固定速率运行,但却提供了更快的数据传输速度。

DDR SDRAM运用时钟信号的上下沿皆传输数据的策略,实现双倍速率传输,大幅提升数据吞吐能力。另外,其引入预取及并行传输等手段,进一步提升存取效率。因此,在高性能运算、网络设施、嵌入式系统等多元需求上被广泛采纳。

为什么需要了解DDR SDRAM时序?

DDR SDRAM时序即为执行读/写动作过程中各种信号间按特定顺序发生之时间关系。精心制定及掌控其时序设计,将保证真正实现内存系统稳健而高效地运作,从而最大化地发挥其性能优势。此外,恰当地调整时序参数亦可在系统设定阶段进行性能优化,从而进一步提高整个系统的运行效能。

由于各厂家DDR SDRAM产品间存在时间偏差,不同品牌的产品需要按照芯片厂商的准确规格来进行配置。精通和熟知DDR SDRAM的时序要求,对电子工程专家而言具有至关重要的意义。这既是保证系统稳定发挥及性能水准的关键因素,也是左右产品市场竞争实力的决定性力量。

如何理解DDR SDRAM时序参数?

为了全面理解DDR SDRAM的时序参数,必需先把握以下几个关键要素。

CL (CAS Latency):指的是在读取操作之前,需要等待的时钟周期数。

- tRCD(Row-to-Column Delay Time):此参数决定了在激活特定行后读取并写入其内数据所需等待的时间长度。

- tRP (Row Precharge Time):行列预充时长,衡量关闭当前行后再次激活相同Bank内异行为止所需之等待时间。

-行激活时间(tRAS):即在预充电完成后,这一行需要再次被激活的时长限制。

- tRC(行周期时间):指完成一次行操作所需的时间。

这些参数对内存读取与存储速度及稳定性有显著影响。针对不同应用环境和硬件配置进行有效调整,有助于优化系统性能,实现最高效率。

如何设计合理的DDR SDRAM时序?

在设计DDR SDRAM时序时,需要综合考虑以下几个方面:

信号品质保障:在设计过程中,必须确保信号质量、稳定及精确度得到充分考虑与保证。

时钟配置:基于主频、倍频与延迟等因素的合适配置,有利于显著减轻内存访存延迟现象。

信号布线:高效的信号布线能够抑制信号干扰及串扰现象,从而改善信号质量。

电源保障:确保稳定的供电,对于保证内存有效运行至关重要。

环境温度:在内存所能承受的工作温度范围内,维持稳定的适宜环境有利于提升内存使用寿命。

经深入分析及测试验证后,灵活调整与优化综合考量,即可构建出适应特定应用且性能稳健的DDR SDRAM时序解决方案。

如何验证和调试DDR SDRAM时序?

实际上,对DDR SDRAM时序进行验证与调试乃是关键环节。验证方法多样,例如:

逻辑分析仪:通过分析各信号波形,判断其是否符合预期要求。

模拟技术:依序运用各种模拟工具开展设计模式的实战推演,以深入洞察各个因素间的内在关联性。

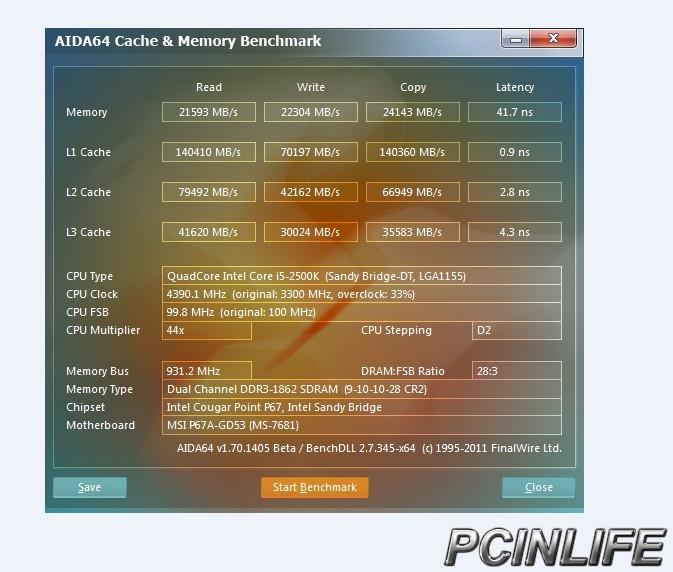

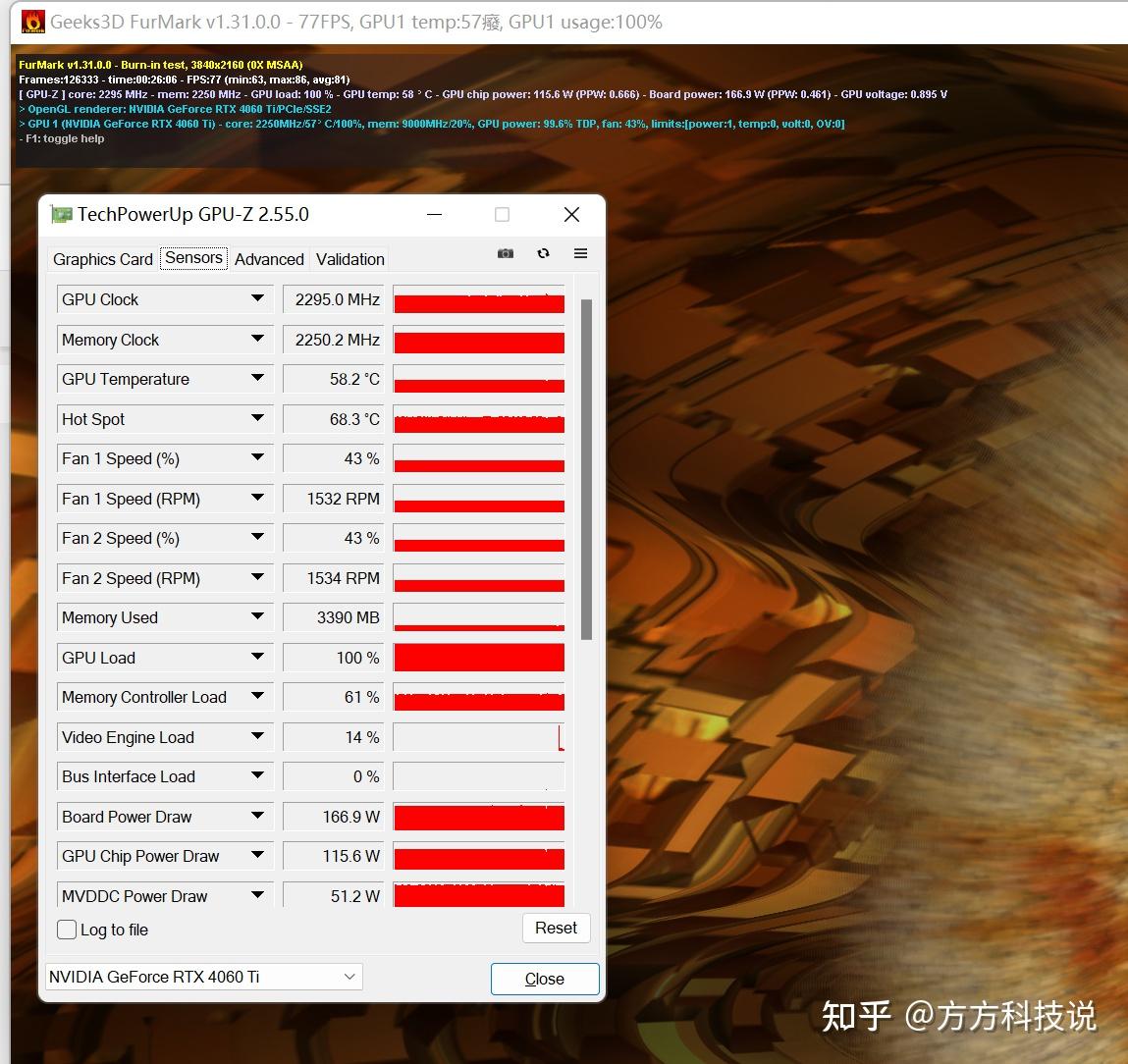

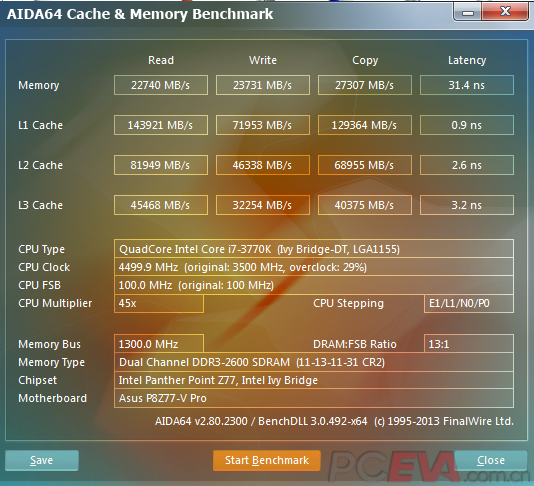

带宽测试:运用精准的带宽测试技术,对内存在读写方面的速度进行客观评估,并依据测试所得数据进行相应优化。

实证检验:通过实地试验及对系统运作状况的考量确定是否需作进一步调整。

借助上述严格的验证方法与实战调试经验融合,能有效地定制出DDR SDRAM正确且高效的时序参数。

结语

总而言之,DDR SDRAM时序在内存系统设计中尤为关键,对于系统性能提升及稳定运作具有举足轻重影响。深入洞察并恰当地使用DDR SDRAM时序参数,有助于提高系统综合性能,以及满足各类应用情境下内存访问速率和稳定度要求。唯有持续学习、实践并深化经验积累,方能在实际工程操作中善用DDR SDRAM时序技术,增强产品市场竞争力。

期望本文能为您带来启迪与帮主。期待您就如何更深入了解及运用DDR SDRAM时序发表宝贵见解。敬请畅所欲言,我们共同探讨。