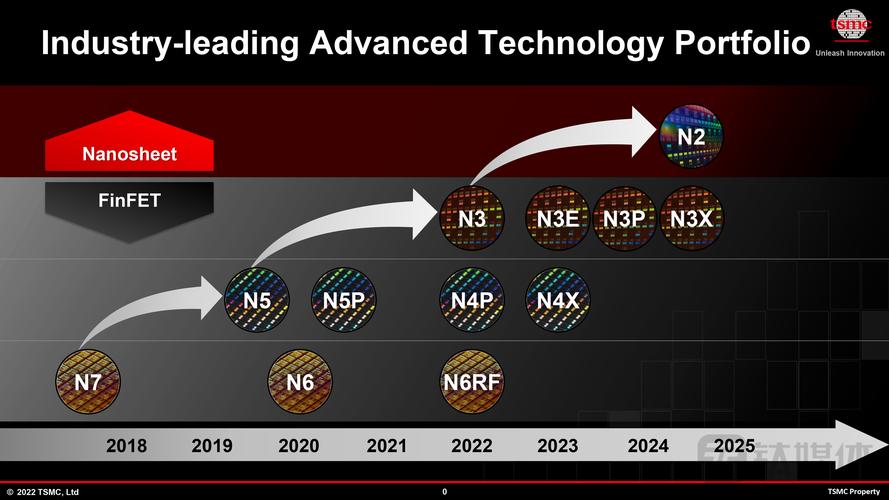

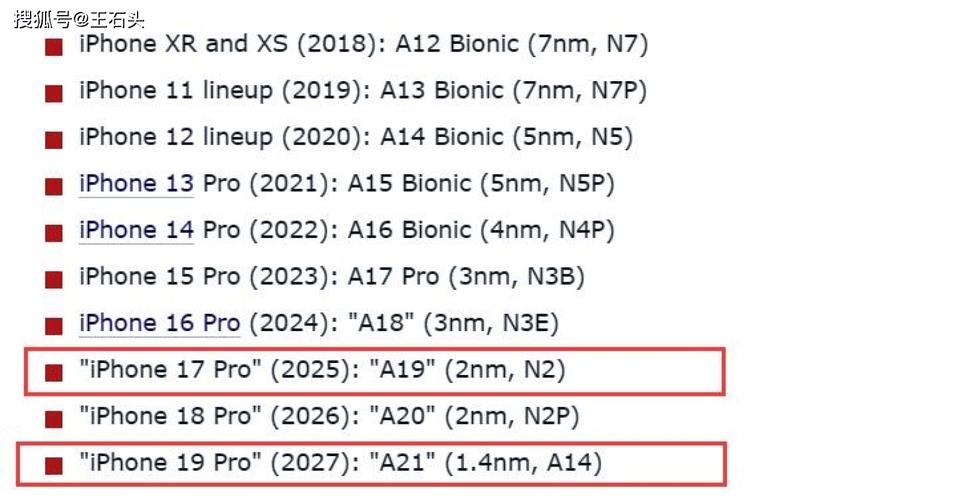

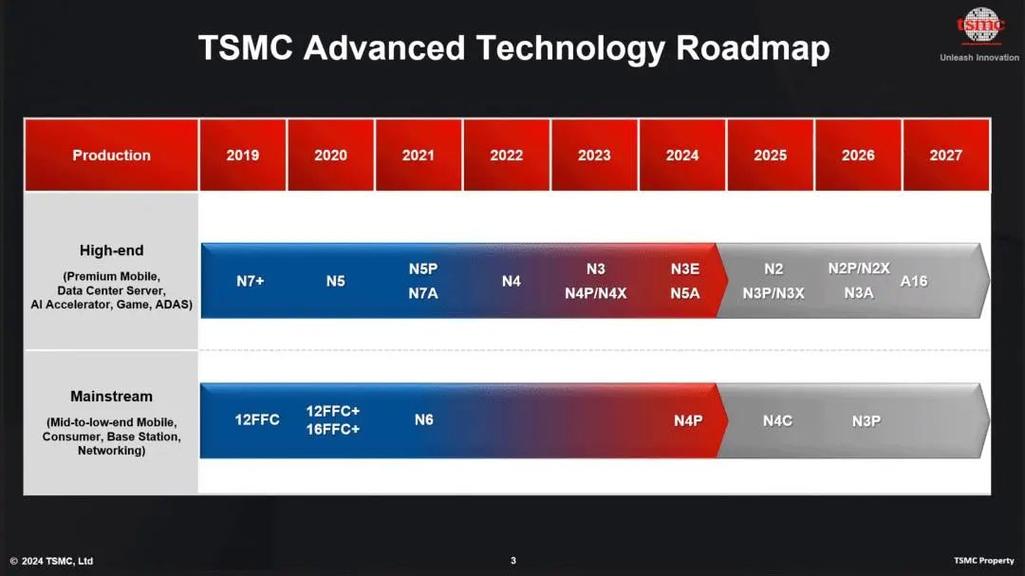

近期,台积电发布了一项备受瞩目的新计划:其N2(2纳米)工艺预计将在明年下半年投入大规模生产。该计划包含多个引人注目的焦点,涵盖了技术革新以及成本因素,这些因素预计将对整个半导体产业产生重大的长远影响。

技术完善进程

台积电正致力于N2技术的优化。在半导体产业,技术的成熟是大规模生产不可或缺的先决条件。这一工作在台积电内部进行,众多工程师参与其中。他们需完成降低可变性和缺陷率、提升产品合格率等目标。这一进程耗时耗力,任何失误都可能推迟量产进度。N2技术的进展是台积电实现2nm量产的基石,其进展对整个项目至关重要。台积电在此项目上投入了大量人力和财力,旨在将潜在问题消灭在初期。

在半导体领域,台积电凭借其深厚的技术积累和多年经验,正致力于技术的持续优化。当前,这些努力正显现出显著成效,公司通过不懈的研发与实验,正逐步克服重重技术难题。

功耗与性能提升

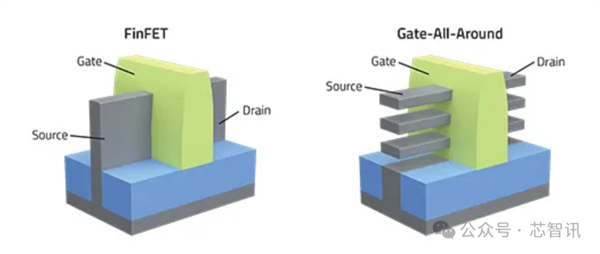

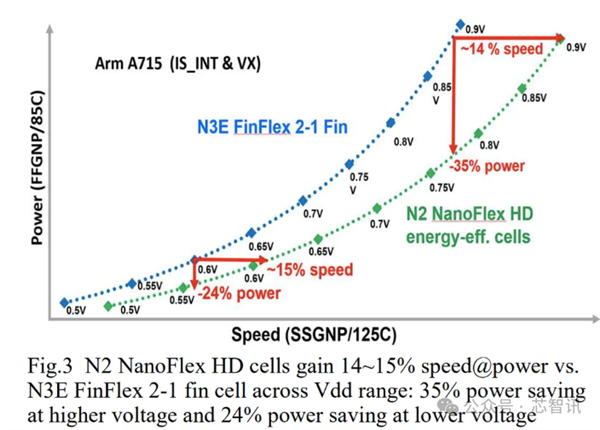

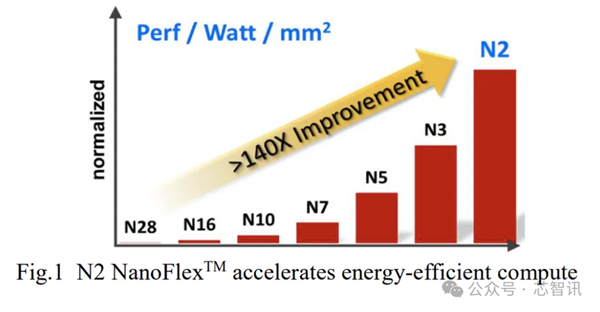

N2制程展现了良好的数据表现。在相同电压条件下,其功耗可减少24%至35%,或性能可提升15%,相较于前代产品具有显著优势。以某款原本功耗为100瓦的芯片为例,采用N2制程后,功耗最低可降至65瓦。这些改进归功于新型全环绕栅极(GAA)纳米片晶体管等技术的应用。这些技术为芯片功耗与性能的提升提供了物理层面的保障。这对于对功耗和性能要求较高的设备而言,无疑是个利好消息,例如高性能计算设备在运行大型程序时,不仅能降低能耗,还能提升运算效率。

技术发展并非仅是数字的增减,其背后反映了科技的进步。新型晶体管结构对电流控制方法等众多领域产生了影响。这些变化汇聚了众多科技工作者的智慧成果。

Nanoflex技术亮点

台积电的Nanoflex技术是N2制程的重要特点。该技术使得同一芯片能够通过不同宽度的纳米片来构建多样化的逻辑单元。例如,窄器件形成的逻辑单元可以用于通用逻辑部分,而宽器件则适合构建CPU核心。这种设计方式显著提高了芯片设计的灵活性。在中国,部分芯片设计公司认为,有效运用这项技术,能在有限的芯片面积内实现更多设计可能性。

该技术的价值亦在于其研发理念的革新。过往设计方案难以实现如此丰富的功能。此技术为新芯片研发开辟了新的路径,使得不同逻辑单元能更优地满足不同功能需求,代表了高效的芯片开发观念。

晶体管架构影响

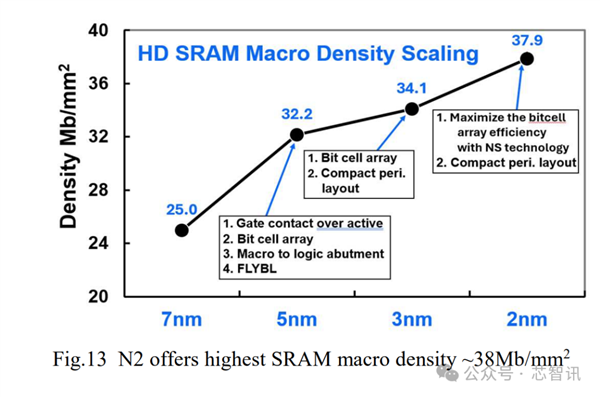

N2晶体管设计显著影响了SRAM的扩展潜力。在先进技术节点上,这种成果的实现尤为困难。该设计优势与DTCO技术相得益彰。观察现实情况,部分存储设备若需大量SRAM,有望从这一技术中获益。企业在研发新型存储产品时,可适度考虑使用基于N2制程的芯片。此架构的优化显著增强了芯片的整体性能。

集成电路技术进步中,晶体管设计的每次改良均具里程碑意义。自晶体管技术问世以来,每一次设计上的革新均助力了整个产业的进步。目前,N2制程所采用的晶体管设计可能标志着行业发展的又一重要转折。

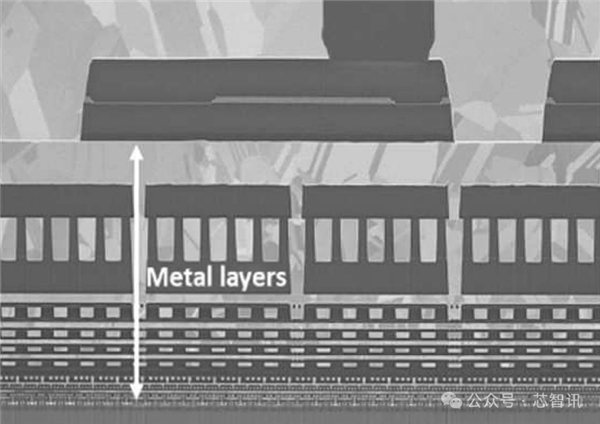

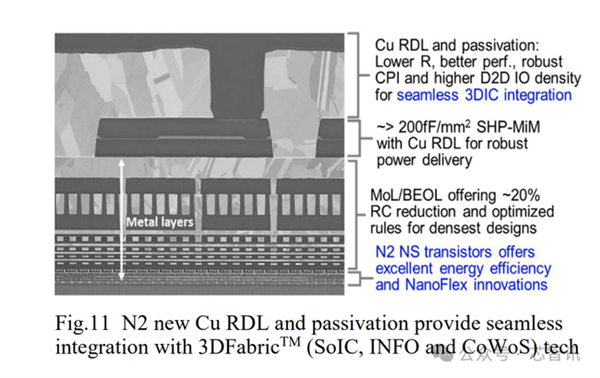

其他新特性

N2制程具备额外的新特性。该制程引入了一种全新的无障碍全钨中间线层(MoL),这一技术使得电阻降低了20%,并提升了性能效率。特别是其应用于高性能计算(HPC)的超高性能MiM(SHP-MiM)电容器,能够提供大约200fF/mm2的电容,这对于提高最大工作频率具有积极作用。这些成就已在业界处于领先地位。

从应用端观察,针对人工智能及高性能计算等领域的设备,新特性确保了其运行更加流畅且效率提升。以执行复杂AI算法为例,更高的工作频率直接转化为更快的处理速度。

面临的挑战

N2制程虽有其挑战。首先,其带来的晶体管密度、性能提升及功耗降低效果较为有限。其次,初期不良率较高,导致成本上升。以12英寸2nm晶圆为例,可切割出的有效芯片成本显著增加。设想一款原本成本为100美元的手机芯片,若采用2nm制程,其成本可能翻倍。这将限制客户对2nm制程的采纳。手机制造商及其他电子产品制造商需在成本与性能之间进行权衡。

台积电面临的问题若未得到妥善解决,将成为量产阶段的关键挑战,进而可能削弱其在行业中的竞争优势。关于台积电是否能够战胜这些困难,读者们有何看法?欢迎在评论区发表意见,并给予点赞及分享。