半导体行业的发展历程中,台积电的2nm制程技术进展备受关注。此技术的进步不仅对台积电的市场竞争力产生重大影响,而且在整个半导体产业链中具有极其重要的地位。

台积电明年量产计划

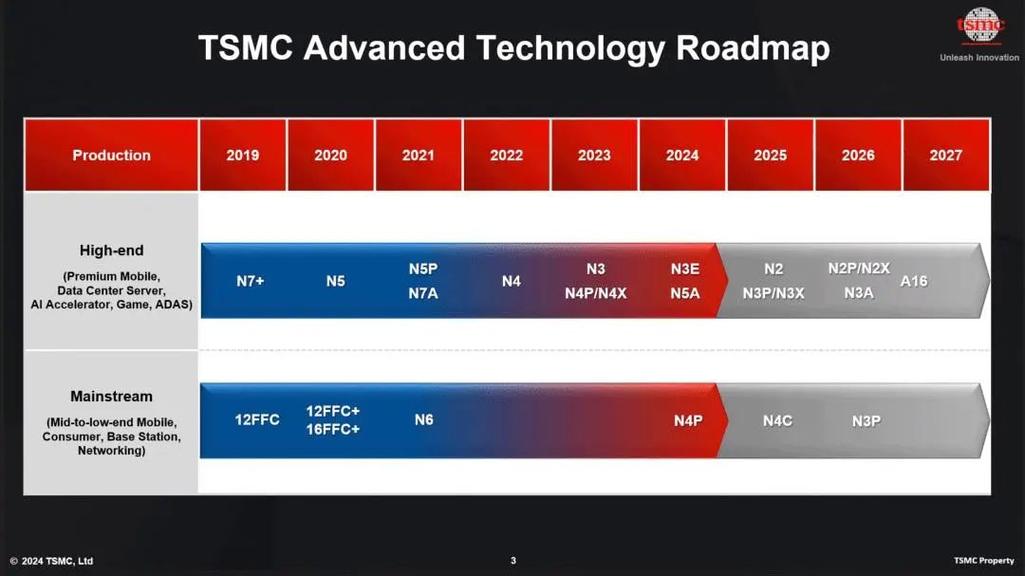

台积电计划在2025年下半年启动2nm制程的大规模生产。目前,半导体领域竞争愈发激烈,众多企业正努力加快进度。台积电的这一举措有望推动行业格局发生变革。该计划的时间节点清晰,若能按期完成量产,将为众多客户带来新的芯片选项。尽管台积电在量产前可能面临诸多挑战,但据目前进度,公司正稳步推进。在技术研发和量产准备方面,台积电总部等区域将是主要活动地,需要投入大量技术人员等人力资源。

从商业视角分析,台积电的收益预测受到显著冲击。提前实现量产,台积电有望在市场上获得更大份额。该战略规划中的2纳米工艺技术,蕴含了多项创新。

正在完善的技术

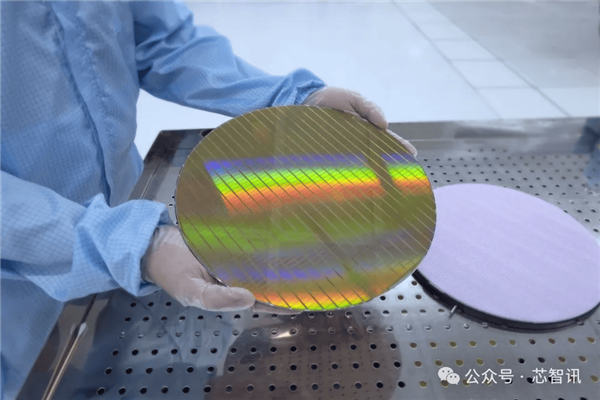

台积电正致力于优化2纳米制程技术,旨在减少波动和缺陷,从而提高产品合格率。在半导体产业,合格率的高低直接影响生产成本和盈利水平。鉴于众多电子设备对芯片成本高度敏感,提高合格率有助于降低成本。目前,该技术正处在密集测试和调整的关键时期,台积电需投入大量资源。

台积电员工透露,公司已成功将N2测试芯片的合格率提升至6%,此举为客户节省了数十亿美元。这一数据充分证明了良率提升带来的显著经济效益。同时,这也反映出台积电在技术研发方面取得了阶段性重要成果。

具体良率提升情况不明

Kim博士表示,台积电已成功将2nm测试芯片的良率提升了6%,但具体是SRAM测试芯片还是逻辑测试芯片的良率提升并未明确。这种模糊性实际上反映了技术进步过程中的复杂性。在2nm工艺节点上,SRAM和逻辑测试芯片的良率提升显得尤为关键。

若能明确哪种芯片的良率得到提升,将有助于外界更深入地理解台积电在2nm制程技术上的具体改进。自1月份开始提供2nm技术的穿梭测试晶圆服务,此次良率的提升或许反映了最新技术的成果。然而,尚无法确切知晓哪些芯片从中受益。

2nm技术的优势

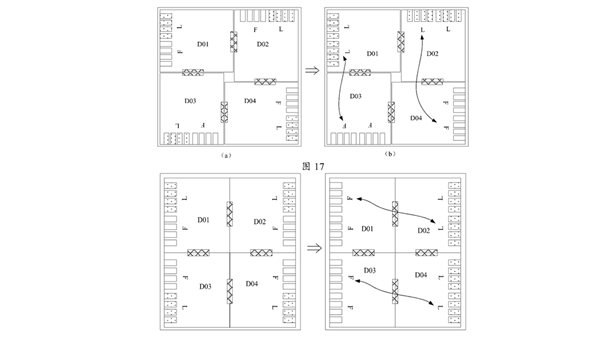

台积电的N2工艺将引入全环绕栅极纳米片晶体管技术。相较于3nmFinFET晶体管,这种晶体管体积更小,标志着重大技术突破。晶体管体积减小,有助于减小芯片尺寸,或在相同尺寸芯片中容纳更多晶体管。

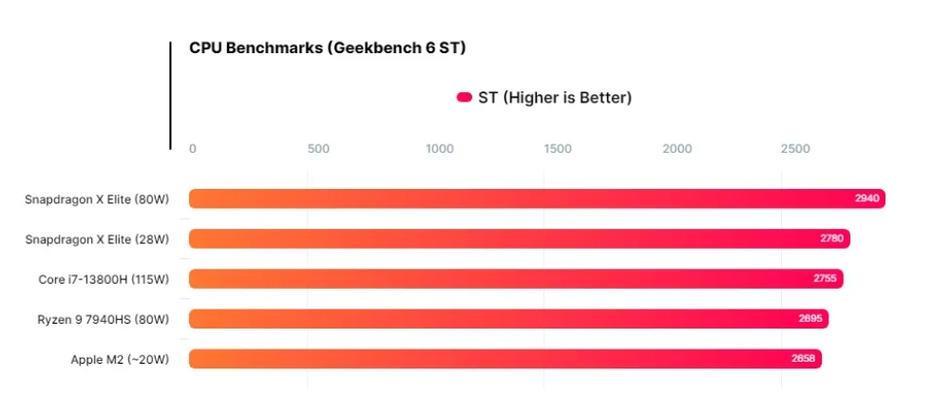

在性能方面,采用N2技术生产的芯片在相同晶体管数量和频率条件下,预计功耗将降低25%至30%。在相同晶体管数量和功率条件下,性能可提升10%至15%,且晶体管密度将提升15%。这些数据揭示了N2制程在性能与能效比上的显著优势。对于电子产品而言,低功耗带来的益处包括电池续航时间的延长等。

新晶体管面临的挑战

GAA纳米片晶体管虽具多方面优势,然而台积电仍需掌握生产高良率新型晶体管的技术。这一过程从理论探讨至大规模生产,实为一大挑战。

这包括构建全新的生产流程和质量控制机制。以晶体管生产为例,必须从头开始研究必要的设备和技术参数,以找到最理想的解决方案。

对客户的价值

提升SRAM与逻辑测试芯片的合格率对消费者至关重要,它有助于降低成本。在激烈的市场竞争中,众多电子厂商追求性能优异且价格合理的芯片。若台积电的2纳米工艺能持续稳定地提供高质量、高合格率的芯片,将对电子产品价格和性能产生深远正面影响。例如,手机制造商若能以较低成本获得性能更佳的芯片,将增强其产品竞争力。因此,众多客户对台积电2纳米工艺的进展充满期待。

众多复杂局面面前,台积电是否能在2025年下半年按期启动量产,并实现既定的良率目标?欢迎各位参与评论交流。此外,也期待大家为这篇文章点赞并予以转发。