1. DDR SDRAM引脚概述

双倍速率同步动态随机存取存储器(DDR SDRAM)是高度高效的内存技术,其引脚配置至关重要。该设备的引脚主要可分为以下几个部分:电源引脚、地线引脚、时钟引脚以及地址/控制引脚及数据引脚。在这些类型中,电源引脚用以维持器件所需的电力供应,而地线引脚则保证了信号的稳定;时钟引脚担负着时钟信号的传输功能,而地址/控制引脚及数据引脚则承载了相关的地址及控制信号以及数据信息。

按照JEDEC规范,DDR SDRAM的引脚布局呈现出稳定一致的特征。因经历多代更迭,每代DDR SDRAM的引脚数量及布局形式也各自有所差异。充分掌握这部分知识有助于理解内存模块运作机理,洞察其优异性能。

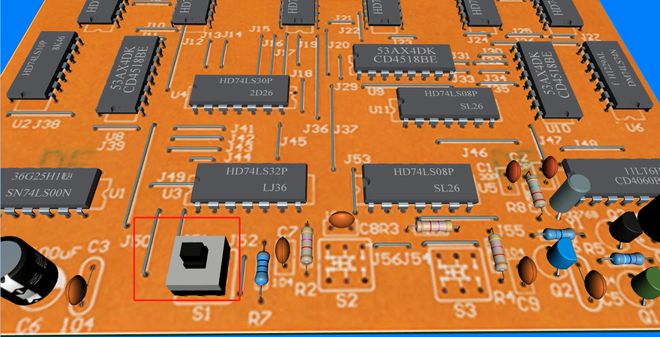

2.电源与地线引脚

电源与地线乃是DDR SDRAM的基本引脚,分为电源引脚(标示为VDD和VDDQ)和地线引脚(GND)两种。链接电源时需精心选择合适的电压源,并对应VDD和VDDQ正确接入,同时牢记厂商规定的工作电压范围,保持稳定供电,明晰各引脚功能,有助于保障内存运作正常;而地线引脚(GND)的目的主要在于引导芯片内产生的杂散信号回到地面稳固信号传输的稳定性。

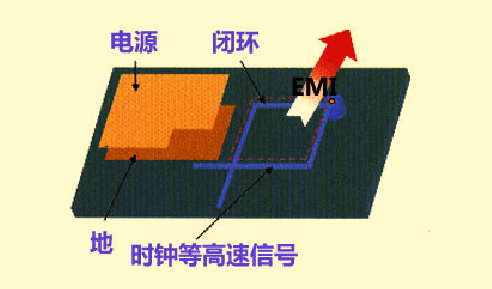

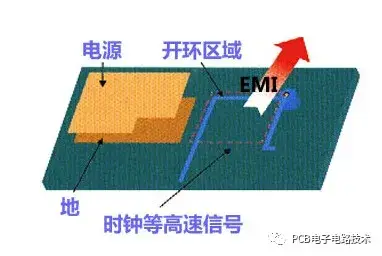

3.时钟与控制引脚

DDR SDRAM的核心组件是时钟与控制引脚。其时钟信号通过CLK信号线交付,以保持内存运算同步且数据读取写入准确无误;而控制引脚如RAS、CAS以及WE则对内存读写行为产生举足轻重的影响。因此,确保时钟和控制信号的正确连接对于DDR SDRAM的正常运作至关重要。

4.地址与数据引脚

DDR SDRAM的关键引脚包括地址及数据。地址总线负责传输存储单元地址,决定操作对象的位置,而数据总线则传递实际数据,保证读取的数据正确无误。准确接通这两根引脚,可让模块准确执行读写操作,进而提升整个系统的性能水平。

5. DDR SDRAM引脚排列方式

依照JEDEC规定,各世代DDR SDRAM均有一定数量与排列顺序的引脚。如DDR3最常用的SO-DIMM封装便有204或240个引脚。而DDR4阵营则普遍选用288针设计。精准的排布能有效控制信号干扰及功耗,进一步增强记忆体模组的稳定性。

6. DDR SDRAM新一代技术发展

随着科技创新和市场需求升级,DDR SDRAM历经多轮演进。由初期的DDR发展至DDR2、DDR3,至今已走进主流的DDR4时代,未来还将引入DDR5等新生力量。每一次更新换代均以提高带宽、缩短延迟和扩大内存容量为主要目标,同时催生出崭新的DDR SDRAM芯片设计及更为精细的引脚布置。

7. DDR SDRAM应用领域拓展

除个人电脑市场外,DDR SDRAM在服务器设备、工作站以及嵌入式系统等领域亦有广泛的运用。面对大数据及人工智能等新兴技术的飞速发展,人们对于存储器的存储容量与处理速率提出了更高的期待,这预示着DDR SDRAM将有望进一步拓展应用范围并发挥关键角色。