什么是DDR3前端总线

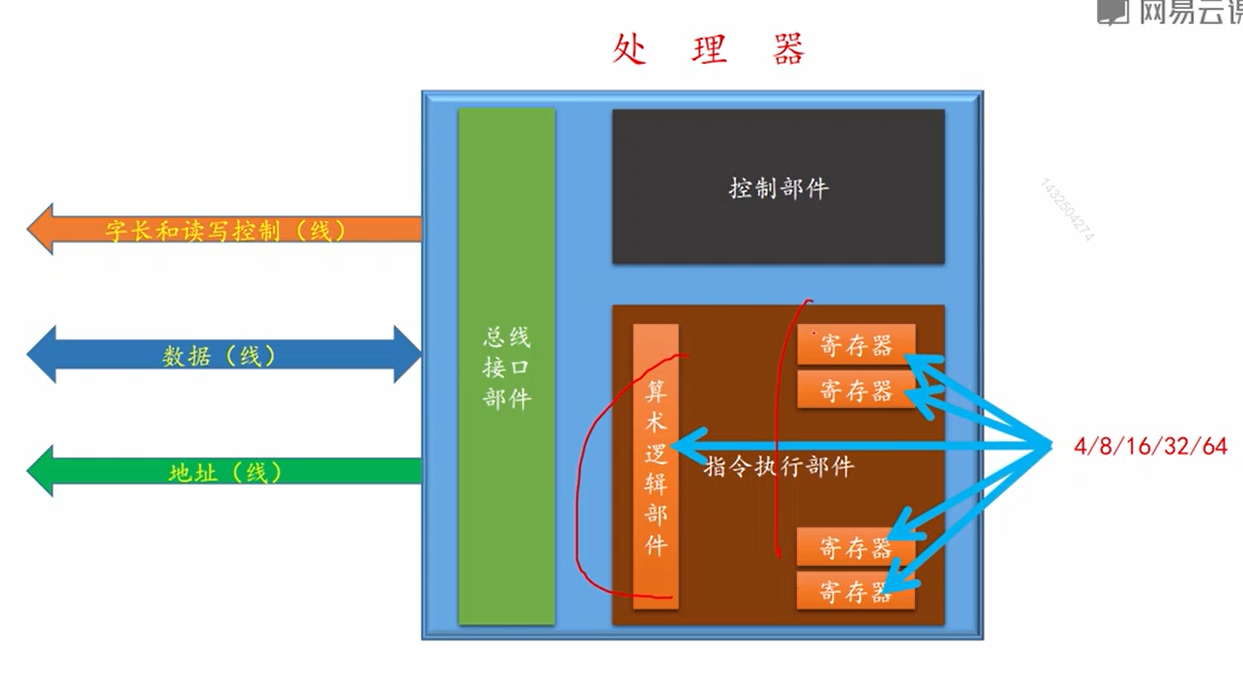

DDR3前端总线,即双数据速率第三代同步动态随机存取存储器中的前端总线,是现代计算机系统中至关重要的组成部分。它扮演着介于内存与处理核心间的沟通桥梁角色,负责数据、指令及地址信号的交互传输。对于这一总线进行深度研究,有助于我们更深刻地认识计算机内数据传输机制以及如何提升其性能。

DDR3前端总线的特点

DDR3前端总线相较于前代DDR2具以下特性:首先,DDR3具备高频率少电压优势,進而提升数据传输速度及降低功耗;其次,其支持大容量内存模组,拓展了系统效能及扩充潜力;此外,DDR3新增预取技术及校准功能,以提高内存访问效率与稳定度。

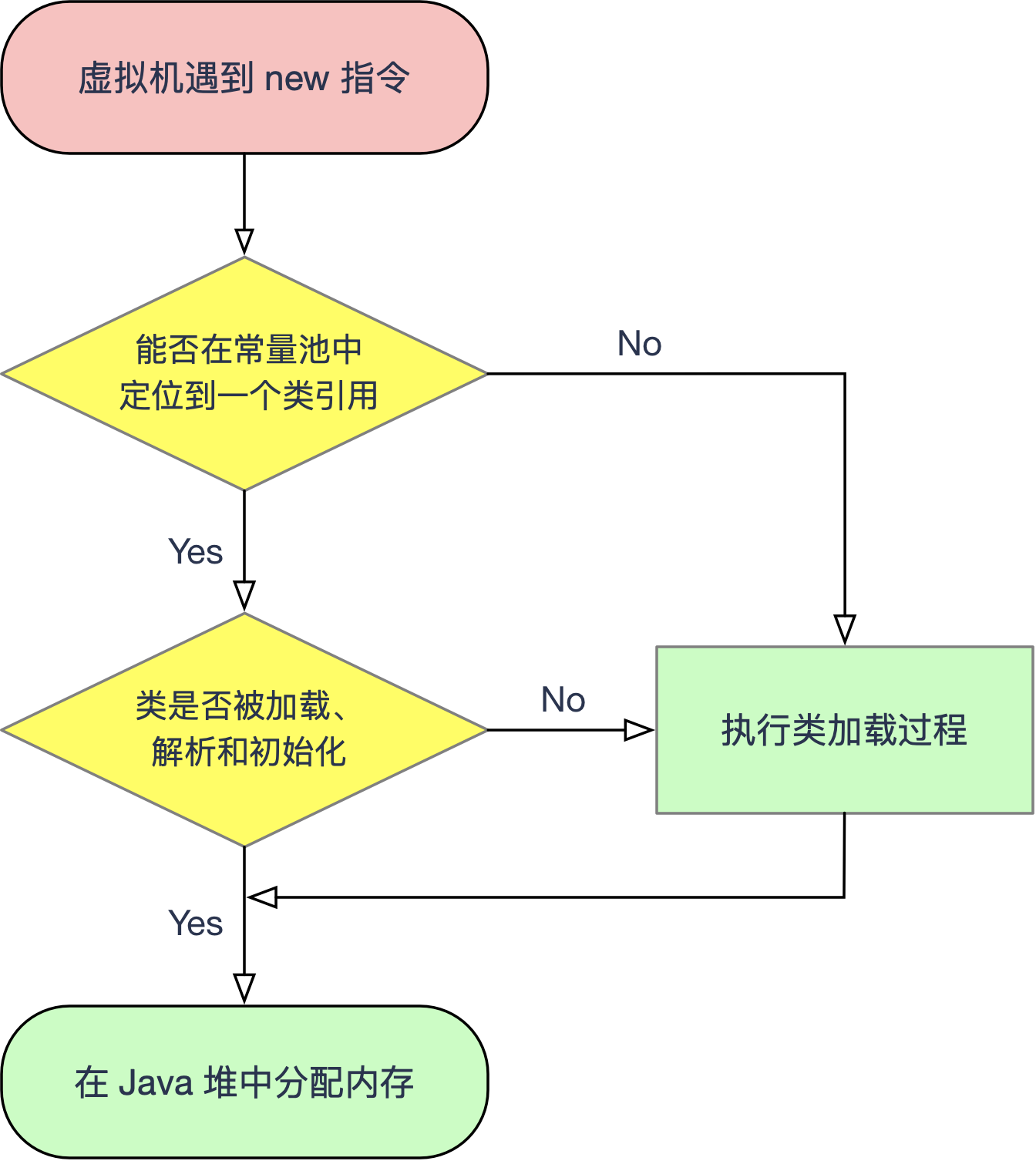

内存控制器与DDR3前端总线

计算机系统中的内存控制器,承担着关键性的任务,例如调度内存访问请求、监管数据流向以及掌控信号传输。衔接基础硬件与内存模块间的DDR3前端总线便是这样关键的物理维度。此一控制器依据处理器之指令给予恰当的读/写要求,并经由DDR3前端总线高速输导向内存模块内。在此过程中,内存控制器也展现出出色的职能,即处理来自内存模块的反馈数据,继而适时地将其递送至处理器或其它设备。

DDR3前端总线频率与带宽

DDR3前端总线频率即单位时间内在总线上产生信号变化的次数,通常用兆赫兹(MHz)表示。频率越高,每秒钟的数据传输量越大。带宽则是单位时间内通过总线传输的数据总量,常用比特/秒或者字节/秒作为单位。那么DDR3前端总线频率和带宽两者间有着怎样的联系呢?提升频率能够放大每秒钟数据传输次数,进而增大带宽;反之,增加带宽便可加速数据传输和提高系统整体表现能力。

延迟与时序控制

在DDR3的前端总线设计中,延迟作为关键要素,会对数据在处理器与内存模块间传递的耗时产生影响。其中,延迟包含了诸多层面,比如CAS延迟以及RAS预充电延迟等。而时序控制,则是在数据传输途径中的所有信号间做到精确无误地按预定时序同步实施。通过科学合理地调整延迟及执行时序控制,可以显著提高系统的运行效能与稳定性。

信号完整性与抗干扰能力

高速数据传输过程中的信号质量及抵抗干扰能力对整体性能具有决定性影响。信号质量涵盖了波形完整性与精确传输程度的保障;而抵抗干扰则要求设备在外在条件波动或受到干扰时仍能保持稳定传输。对于DDR3前端总线而言,实现信号质量提升需考虑到布线设计、端接成套、信号分层等多方面。

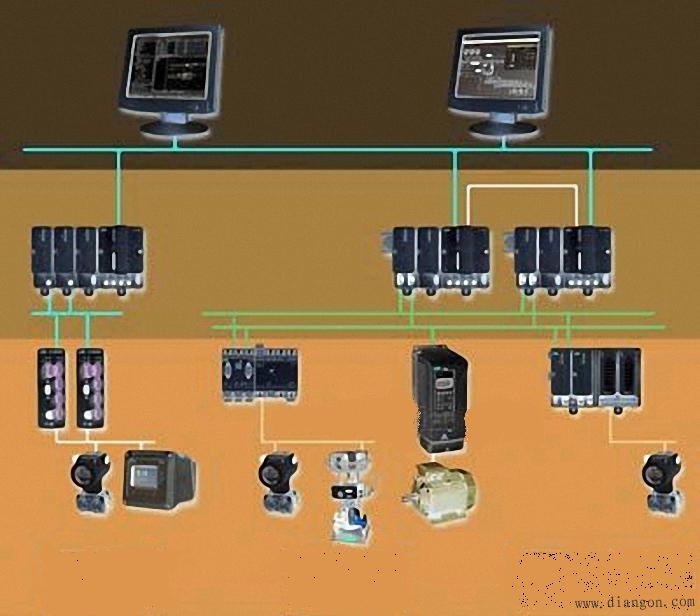

主板布局与电磁兼容

为实现DDR3前端总线支持,板载设计需重视布局规划与电磁兼容性。改进主板布局可通过优化内存接口布局、精简信号传输路线以及削弱串扰等举措实现;同时,在电路板(PCB)设计中引入电磁兼容性可显著降低并解决电磁辐射与相互干扰的问题。

未来发展趋势与挑战

伴随着科技进步,DDR4及DDR5新型内存规格陆续推出并逐步占领市场。然而,面对即将涌现的新一轮科技革命,DDR3不免身处科技更迭、节能减排以及数据传输速率提升的巨大压力之下。立足当下,能否妥善处理性能与能耗之间的关系、进而提升数据传输效能和稳固性将成为企业面临的核心课题。