什么是DDR3前端总线

DDR3前端总线作为计算机内存体系中的关键部件,负责衔接内存模块与主板间的数据交换。DDR3内存规范的前端总线一方面扮演了CPU与内存模块之间的介者角色;另一方面,该组件在现代计算机系统中发挥着决定性作用,无论是其性能还是稳定性都会直接影响到整体系统的运行效能。

以DDR3前端总线为例,由一系列精密协议和信号传输技术驱动,旨在进行高效而迅捷的CPU与内存模组间的数据交互。其意义并非仅限于简单的电路连通,而是成为了整个计算机体系的关键节点,即数据传递与处理的中枢。深入理解其工作原理及方式,将助我们深入洞悉计算机系统运作的奥秘。

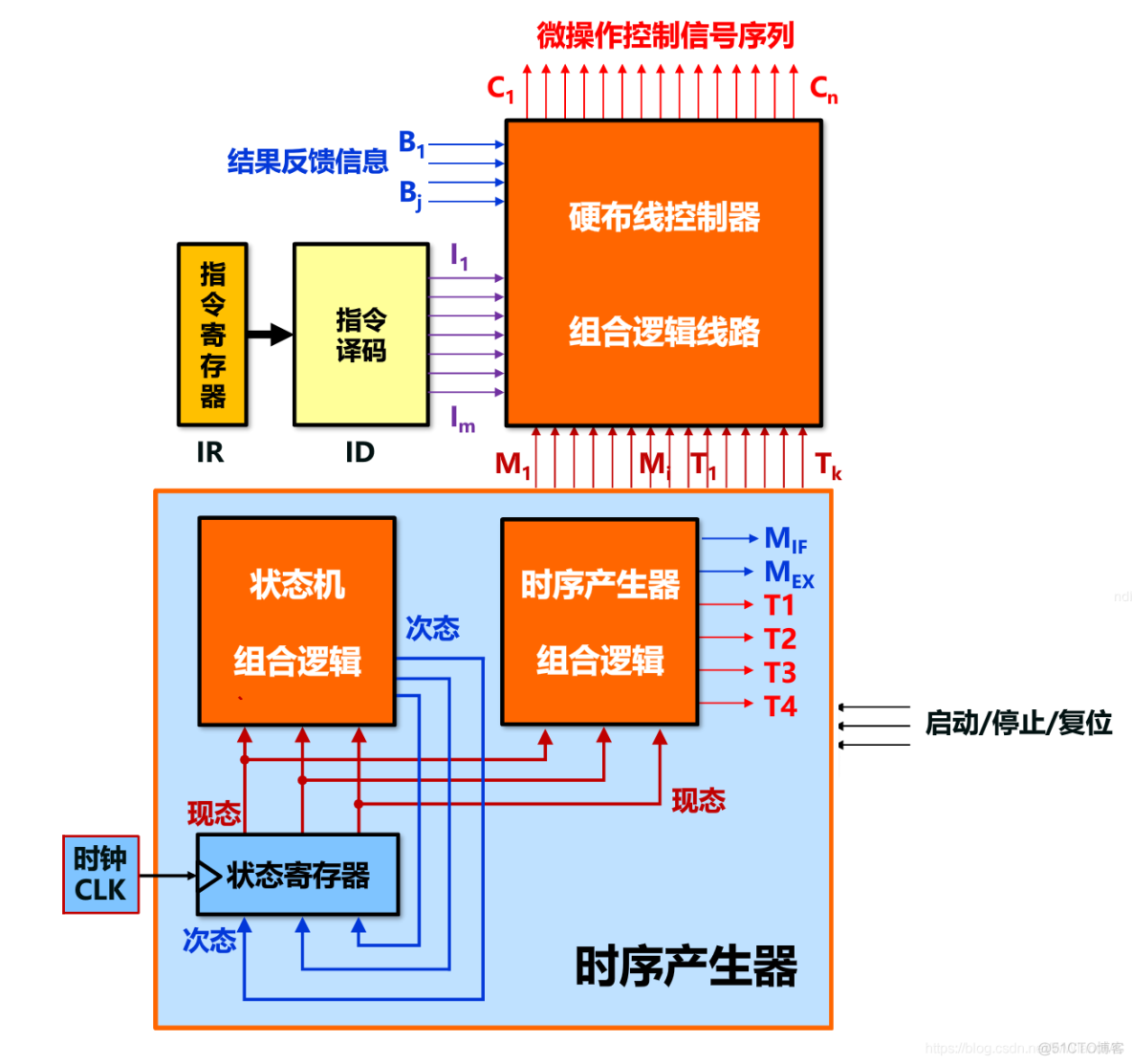

DDR3前端总线的结构

典型的DDR3前端总线主要由地址总线、数据总线及控制信号三大元素构成。其中,地址总线负责传输内存模块的地址识别信息;数据总线担负起实际的数据运输工作;而控制信号则囊括时钟信号与读写信号等,通过对其进行精细调控,实现数据传输流程的顺畅运行。

在DDR3型前端总线路径中,地址及数据总线具有关键作用。地址总线确立了内存可寻址范围;数据总线则负责实际数据传输。二者协力实现CPU与内存间的高效沟通。

DDR3前端总线与系统性能

DDR3前端总线对计算机系统运行速度及稳定起到重要影响。高效且稳健的DDR3前端总线能提升综合性能,提高数据传输效率,减少程序反应时间。然而,若该总线出现问题或瓶颈,将会降低系统运行速度并出现卡顿现象。

在构建计算系统过程中,需重点关注 DDR3 前端总线的功能需求,科学规划硬件配置及链接模式,以便让系统潜在能力得以全面释放。唯有保证其稳健高效运行,方能实现最佳效果。

优化DDR3前端总线性能

为优化DDR3前端总线效能,主要应在以下几个层面进行优化研究。首先,硬件设计环节中,慎重安排PCB板上器件位置及选材至关重要,有助于改善信号传递品质;再者,时序设定方面,适当调控时钟频率与延时时间等参数,能够优化数据交换速度;此外,固件优化同样不可忽视,适时更新 BIOS 与驱动程序,均可对DDR3前端总线效能产生积极影响。

结合多方考量的硬件构造,时序调控及纯软件品质优化,同时依据特定需求以灵活调整与改良,已被证明是显著提高DDR3前端总线性能的切实途径。

未来发展趋势

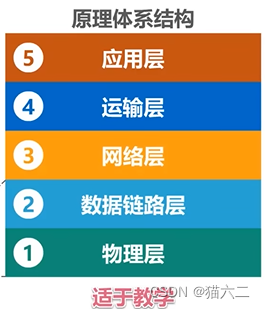

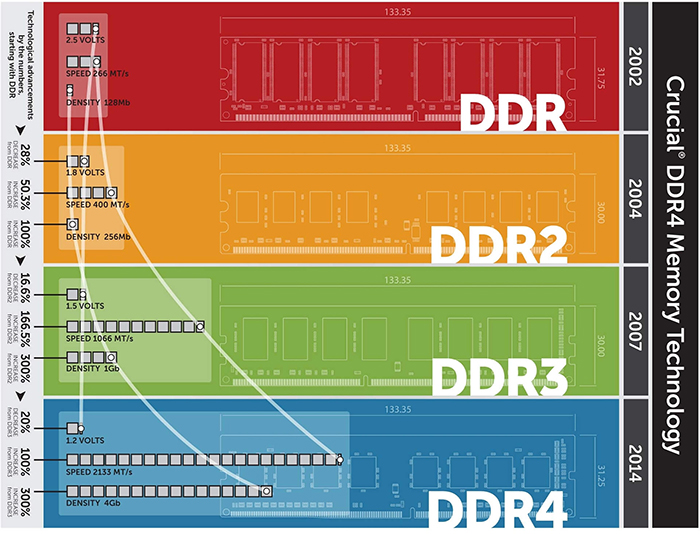

伴随着科技创新持续推进,DDR3前端总线将迎来变革,新的、更为尖端的记忆体规范如DDR4和DDR5等将逐步替代它。对比旧有标准,这些新型规范在带宽与功耗性能上均取得明显改进,因此在不久将来,我们或许能看到它们在计算机系统中的广泛应用,以及不再使用过时的DDR3标准。

即便如此,在过渡阶段,仍有大量计算机设备采用DDR3内存,而大部分应用需求并不迫切看重性能表现。因此,可预见的未来一段时间里,DDR3前端总线还将会在特定领域中得到广泛运用。