近年来,随着科技飞速发展,计算机内关键部件——内存的性能及可靠性日益突显其重要性。DDR3 2400内存时序作为极具潜力的产品,其驯良的性能倍受关注。本文将全面剖析DDR3 2400内存时序的相关知识,包括时序概念、参数设定和优化技术等方面内容,力图帮助广大读者深入理解此领域奥妙。

时序概念

DDR3 2400内存的“时序”明确规范其执行数据读写功能所需严格遵守的时间顺序和原则。在计算机系统构筑中,内存控制器依靠特定的时间序列传递接收信息,以此保障数据传输和处理的准确性。由此可知,对时序的深入理解需要综合考虑繁杂的参数及规则,且需精细调控和优化。

诸多参数构筑了时序系统,包括CL(从内存列地址标识到产生数据之间的延迟)、tRCD(行地址至列地址转变所需时间)、tRP(主存单元预充电时间)和tRAS(行有效触发器启动时间)等。以上参数相互影响,直接决定着内存的性能表现。

对于DDR3 2400规格存储设备,数字"2400"表示其工作速频率高达2,400MHz,从而使每秒可处理的读写次数增加至2.4亿元次。然而,时序设定需严格符合要求,以适应配套的内存控制芯片和处理器高速运作,最大程度地提升存储效果。

时序参数详解

CL(CAS Latency):数值愈低表示存储器反应速度越快。如 DDR3 2400MHz,其典型 CL 值约在11至12个时钟周期范围内。数值偏低固然能提高数据获取效率,然而对于内存与主板的品质也有着更加严格的要求。

tRCD(Row Address to Column Address Delay):表示DDR3 2400内存命令行地址到列地址间的延迟时长。建议数值在11至15个clock周期范围内为佳。

TRP(预读刷新): tRP在DDR3 2400内存在于约11至15个时钟周期内,科学设置能显著提高数据读取速度。

延迟加载周期(tRAS):作为暂驻激活时间,例如采用DDR3 2400规格的存储器,其典型数值在大约27至39个时钟周期之间。通过精细调整这些参数,我们能够实现读写速度的相对平衡。

优化DDR3 2400内存时序

确证板载支持:为充分释放DDR3 2400 MHz内存性能,选择适配的主板至关重要,须保证其与该频率完美兼容并配备充裕电源和高效率散热设备。

精细调整BIOS设置:针对DDR3 2400内存特性,优化BIOS各项时序参数,从而提升整机性能水平。

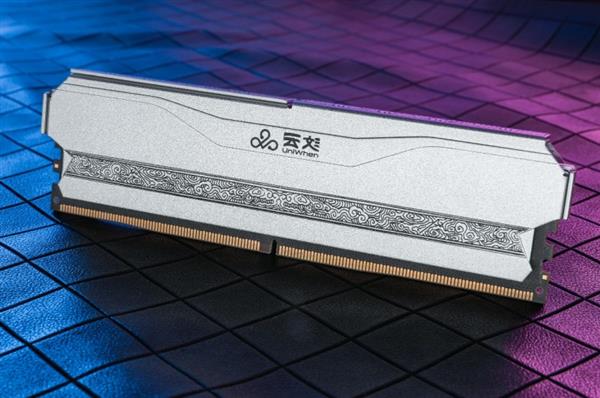

瞩目显赫:精选高稳定性的DDR3 2400内存,具备出色的耐久性与散热效果,品质卓著。

性能优化:采用高端处理器,有效激发DDR3 2400内存潜能,提升整体操作响应速度与顺畅性。

概论而言,DDR3 2400内存的时序设置对电脑系统效能具有关键影响力。深入熟悉并适时调整这些参数,对系统稳定性及运算速度的提升举足轻重。随着知识积累和实践操作的逐步完善,我们将能够更为高效地利用这一技术,使电脑整体性能得到提升。