什么是DDR时序图

在飞速发展的电子行业内,DDR(双数据速率)内存已成为主流存储设备之一。DDR时序图在其设计与调试过程中起着关键作用,它是一幅生动描绘DDR内存读写时序关系的图表,便于人们理解各项信号间的准确时间关系,进而提升DDR内存的性能。

时序图的组成

DDR时序法规则包括了核心的时钟信号、定位内存单元的地址信号、启动读写操作的控制信号及承载有效数据的数据信号等关键元素。在它们协同动作之下,构成了完整的DDR内存读写过程。

读操作时序

在DDR时序图中,读操作的复杂和精确程度毫不逊色。首先,每当系统需要执行读取操作,控制器即向DDR内存发出读命令,同时附带相应的地址信息。其次,在下个时钟周期内,内存利用该地址信息寻找到适当位置的数据,并开始将其输送至数据总线。待再向下一个时钟周期之后,CPU即可从数据总线上获取这些重要数据。整个流程严格依照预定的时间序列进行,任何微小的偏差均有可能影响读取结果。

写操作时序

相类于读取操作,写入操作亦须严谨执行特定时间序列。在系统要求执行写入指令时,控制器向DDR存储器发出写信号,同时附上需写入的数据及地址信息;紧随其后,在下一个时钟周期内,存贮器接受数据并传输至预定位置;最终,在再次回到的下个时钟周期中,系统会确认写入操作已完成,并发出结束信号。在此过程中,各个环节间的时间关系必须绝对精确无误。

校准与优化

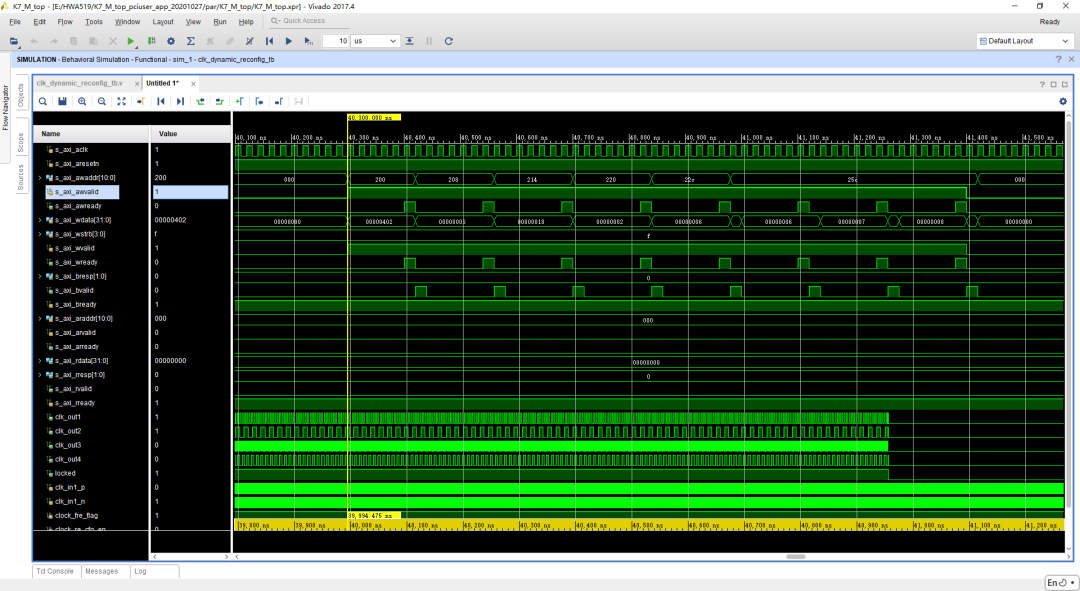

实际应用中,DDR内存可能因为硬件设备及布置等原因产生一系列问题,例如时序波动、延迟增大等。因此,工程师需借助DDR时序图进行精确调整与深度优化。他们依据具体情况调整各信号间时间关系,以保障数据传输过程中的稳定性和可靠性,展现其专业技能。

故障排除

在处理系统读写异常或运行效率降低等状况时,DDR时序图成为关键的故障排查工具。工程人员可依据其上各信号波形是否符合作业规范来定位问题源头,进而实施针对性改善策略。故而,具备熟练的DDR时序图解析能力对确保系统连贯、高效地运转具有重要价值。

未来发展

伴随着科技日新月异的飞速进展,DDR存储器作为计算领域关键部件,其各项指标如效能、能耗等正日益精进与强化。展望未来,我们可能看到更多更尖端的智能、自动化分析工具有望出现在DDR时序图领域,为工程师们提供更为高效便捷的调试及优化服务。与此同时,在蓬勃发展的人工智能、物联网领域,对高速高效的存储器访问需求亦将日益增长。