如今数字电路的设计领域,Xilinx平台以及其所选用的FPGA芯片得到了广泛的运用;尤其是DDR3这种高效的内存模块,在数字系统设计中的地位不可忽视。本条目旨在详细介绍借助Xilinx平台进行DDR3设计的相关教程,其中涵盖了基础理论、设计流程、时序分析、约束设定和模拟验证等环节,以期明确阐述该技术的应用及效果。

1. DDR3内存简介

DDR3新型内存为具备高速度、大存储容量与低能耗特色之双数据速率同步动态随机存取存储器(SDRAM),相较DDR2在频宽及能效两方面均有所突破,其更佳表现扩展至诸多数字系统设计领域,如图像处理、视频编码解码以及网络通讯等。对于在Xilinx平台上进行DDR3设计的用户而言,理解、掌握该内存的基础结构与工作原理尤为关键。

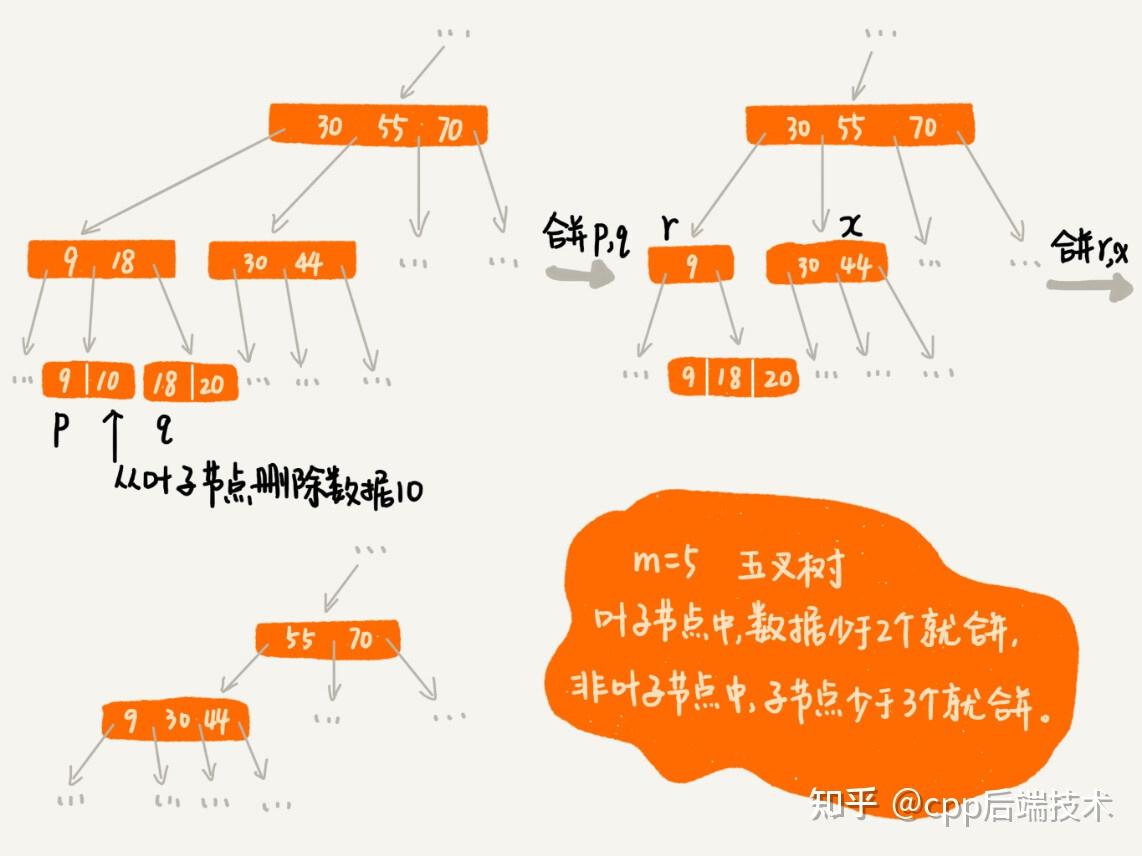

DDR3内存主要包括存储芯片、控制器及物理接口等组件,存储芯片用于数据储存,而控制器承担着数据传输调控之责,同时物理接口则负责连接控制器与存储芯片。因此,在使用Xilinx平台进行DDR3设计时,需深入理解各组件的功能及其交互配合,以确保设计的稳定性以及各项性能指标的优越表现。

在实际运用DDR3时,需充分考虑信号完整性、时序匹配以及功耗管理等问题。为确保成功设计,必须掌握基本数字电路知识且具备出色的逻辑分析及问题解决技能。

2. Xilinx平台概述

作为全球顶尖的可编程逻辑元件(PLD)供应商,Xilinx以其FPGA产品享誉业界,被广泛运用在通信、工业控制以及医疗器械等多重领域。Xilinx平台上的DDR3设计,其核心在于选择适当的FPGA芯片,并借助公司所提供的开发工具完成设计及验证工作。

作为赛灵思公司研发的综合开发环境(IDE),Vivado Design Suite为用户提供了从设计至验证的全环节服务。利用这款工具,工程师能够在短时间内完成包括逻辑综合、布局布线以及时序约束设定在内的各项复杂任务,从而实现对多样化数字系统的高效设计与调试。

除了Vivado Design Suite之外,Xilinx还特别提供了丰富的IP核库及开发板支持包,极大提升了用户在其平台上构建DDR3设计的效率。此外,Xilinx活跃的技术社区更是宝贵资源,为广大工程师们提供了交流互助,携手共进的平台。

3. DDR3设计流程

在Xilinx开发环境中完成DDR3技术的研发设计,常规步骤如下:明确规格要求->设备选择->电路图设计与验证->限制设定和转换逻辑综合并操作->物理布局和布线特性分析->电路仿真确认运行情况->实机测试以印证设计成果。

其过程可概括为:首先依据项目具体需求确定适宜的DDR3规格,并挑选相应型号;其次,在Vivado设计平台上绘制原理图,设定满足DDR3运行时序要求的时序限制;接下来进行逻辑综合与布局布线操作,确保电路功能准确无误的同时提升整体性能。

仿真验证乃DDR3设计之关键环节,可保证电路功能的正确性与稳定性。此外,硬件平台下板验证同样不可或缺,确保设计达到预期效果且满足实际应用需求。

4.时序分析与优化

时序分析乃DDR3系统设计重要一环。在Xilinx环境下,如何精准把握系统时钟频率及数据传输速度等参数,并依据具体需求开展时序调整与优化至关重要。

借助Vivado底层软件的Timing Analyzer功能,我们能够全面地分析电路的时序状况,准确测定潜在的时序违例问题。借助此分析工具,我们能针对其给出的详细报告,有效地优化关键路径,并对时序设置做出精准修正,从而满足DDR3内存控制器严格的时间频率要求。

实际运用过程中,时钟延迟插入及数据传输延误等因素会直接影响体系的稳定性和性能表现。对此,从事时序分析与优化工作时要格外慎重对待每种延迟情况,确保整个系统的稳定高效运转。

5.约束设置与调试

约束设定乃确保数位体系流畅运作及满足性能需求的重要步骤之一。在Xilinx平台实施DDR3设计时,应根据各信号通道特性,设置适当且有效的约束条件。

利用Vivado中的Constraints Wizard工具,工程师可便捷地创建各式约束条件,满足实际应用场景需求。同时,设定约束时应充分考虑信号路径间的相互作用和影响,以免因冲突引发系统运行异常状况。

调试乃数字系统设计核心流程之一。DDR3设计期间,时空违例及数据错谬等诸多困扰,唯有借助诸如逻辑分析仪与信号探针等设备进行细致调试,方能找寻并平息问题。

6.仿真验证与调优

虚拟验证乃保证数字化系统具备正确性与可靠性的实用方法之一。使用如Xilinx平台,可运用ModelSim等工具对DDR3中的电路功能展开验证,同时监控各个信号变化是否符合预期效果。

仿真技术可提前识别并修正潜在隐患,且能够监测及评估诸如最大工作频率、延时等的电路关键性能参数。依据仿真成果,我们还能对电路进行更为精准的优化改进。

另外,仿真过程中可模拟电路在特定环境下的运行状况,包括临界路径拉长和数据传输异常等情况。这些仿真结果将有力地支持实际硬件开发中的调试工作。

7.总结与展望

通过深度剖析Xilinx平台与DDR3综合设计教程,我们对DDR3内存基础理论及其在数字处理器体系中的关键角色、Xilinx平台以及Vivado软件工具的操作技能、DDR3设计的潜在过程和关键组成部分(例如时间序列分析、约束设定以及模拟测试)有了更清晰且深刻的认识。

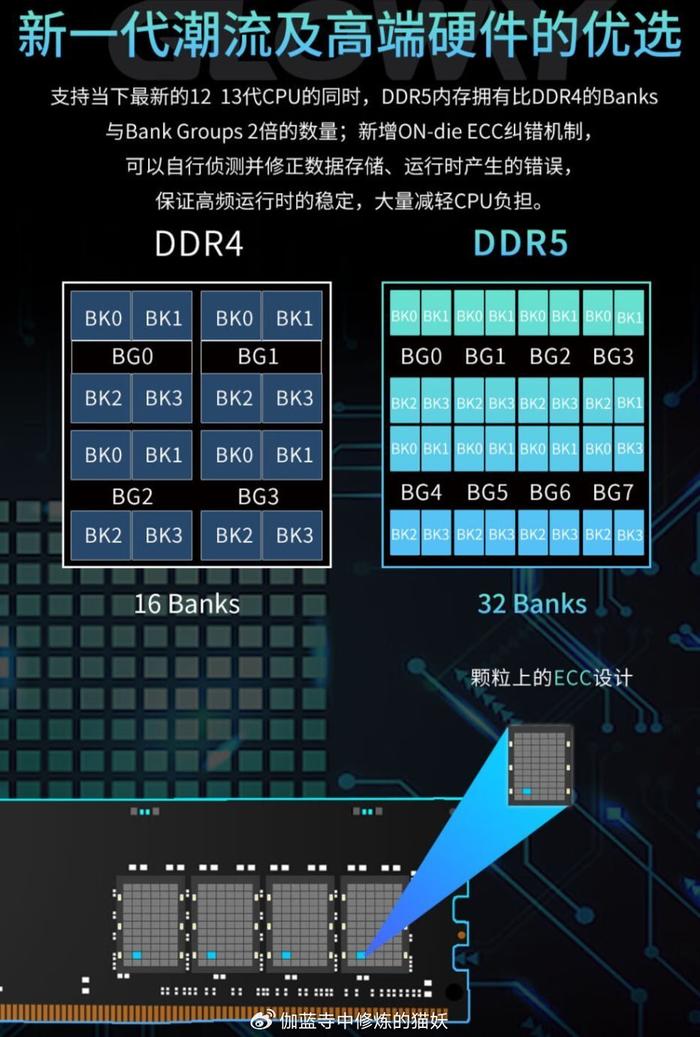

随技术进步,DDR4内存逐渐取代DDR3成为主流款式,因此,我们可预期Xilinx平台的DDR4设计指南将在未来成为热门课题。

透过对本文知识的深入解读,我们能够更精准地把握Xilinx平台DDR3设计技巧,从而深化技术能力,并将所学运用到实践项目中。