DDR3控制器时序概述

DDR3控制器时序便是指内存DDR3运作过程中,控制单元与存储电路间需遵从的时间系列准则。精确精细地调节此规则,对提高设备操作速度、保证稳定运行以及优化能源消耗都至关重要。其中,时序包含了预充阶段、读取写入操作的延迟时间以及时钟频率等诸多要素,接下来就分别来详细阐述这些概念。

预充电时序

预充电乃DDR3存储器运作之核心步骤,为保证存储器芯片具备适当工作状态而实施。预充电工序包含了预充指令的释放,预充电持续时间及其成功后的延迟等环节。精心设定适当的预充电时序能显著缩减读取与写入动作的延迟,进一步提升数据传输之效能。

预充命令的发送通常由控制器指挥,需统筹信号传输延时与命令解码时长等因素,以确保存储芯片正确回应。预充时长需依据特定存储器芯片特性及工作频率而定,太短易引发读写失误,时间太长则将对系统反应性能产生不利影响。另外,预充结束后还需经一段延迟方可进行后续读写,这亦是控制器时序设计所必须关注的重点考量因素之一。

读写延迟时序

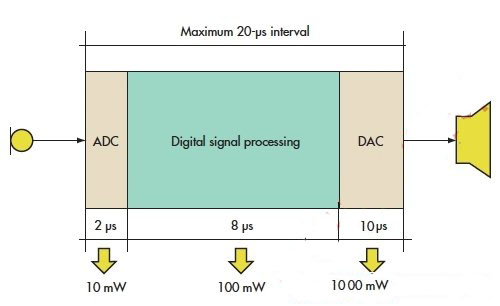

读写延迟乃指从控制器发出读写指令至实际数据传输启动之间的间隔时间,其中涉及了指令信号传输、地址解码以及数据传输等诸多环节的时延。通过优化延迟时序设定,可大大缩短数据传输间歇并提升系统运行效率。

指令信号传输延迟,系指控制器向内存下达读写指令所需的时间,其中涉及信号线路传送、驱动能力等影响因素;地址解码延迟,则是内存芯片接到指令后解析地址,以及定位至特定存储单元所需的时间;而数字传输延迟,即实际数据在总线上传输抵达目标位置所耗费的时间。这些过程中的各种延迟因素环环相扣,需协同调整,以实现性能的最优效果。

时钟频率与时序关系

DDR3内存在运行速度方面主要依赖于外部晶体震荡器所产生的时钟信号,且控制器需通过精确设置时序以适应各频率段下的数据传递需求。为了实现高效运作并保证信息传送的精确与稳定,时序的各个参数必须严谨把控。

随通信速率提升,各时序参数间的牵连日益繁复而敏感。如高频率条件下,须缩减预充时间且降低读写延时而满足高速数据传输需求,同时兼顾信号完整性及噪声抑制问题。为此,制定DDR3控制芯片时序布局时,需周全评估各项参数间的平衡与协同效应。

校正与优化

DDR3控制器的时序设置并非固定不变,实际应用过程中易受外部干扰和硬件磨损等因素影响,导致偏差出现。为确保系统稳定性,需开展必要的校准和优化工作。这将涉及到对关键参数值的精细调整以及固件版本的适时升级等措施。

在校正和提效过程中,针对各种参数的精确调节需依据实际情况而定,并以测试结果作为有效性的验证标准。如,借助特定的测验设备对系统展开全方位评估,再据此有针对性地进行改进以保证DDR3控制器的稳定性能及迅速响应潜在问题的能力。

功耗优化

除了保证性能稳定性,DDR3 控制器的设计还需要重视能耗优化。充分利用资源和降低能耗既能节省能源成本又可以减轻系统负荷与提升设备可靠度。

功耗优化需在多层面进行,包括调低工作频率、调节供电电压以及应用低功耗模式等措施均可显著减少能耗。然需在设计初始阶段即兼顾功耗优化战略的制定,根据实际使用环境进行适宜的选择与配置。

抗干扰能力

鉴于DDR3内存工作环境常受电磁辐射和射频干扰影响,导致数据传输质量不稳定且易受干扰。因此,提升系统的抗干扰性对于保障数据传输质量至关重要。为此,在DDR3控制器设计阶段,必须采取有效措施以抑制干扰源头,确保数据传输优质可靠。

抗干扰性能涵盖了诸如屏蔽设计、过滤技术与地面处理等领域。采用恰当的PCB电路安排,精选优质元器件和强化接地连接等措施,可大大增强系统的抗扰能力。另外,借助专业测试工具开展系统骚扰评估并根据反馈结果对设计作必要调整也是有效途径之一。