什么是DDR3时序图

本文所探讨的DDR3时序图,详尽地反映了DDR3内存运行过程中各种信号的精确时间关系。对于整个计算机系统的性能而言,内存的读写速度有着举足轻重的地位。借助于DDR3时序图,我们能够深入理解内存模组与主板间的信息传递机制,从而进一步优化内存性能。在学习和把握DDR3时序图的基础上,我们有望深入解读内存模块的相关运作,及各类信号的传输路线,以及不同频率时钟之间的相关性,从而为提升内存性能提供宝贵的参考依据。

时序图中的关键参数

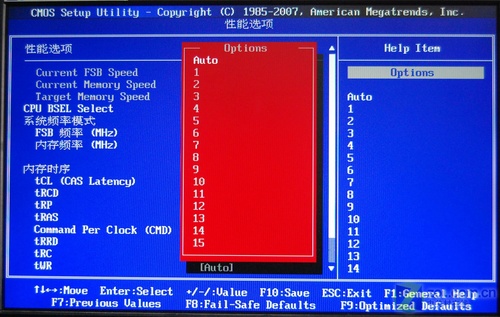

DDR3协议中的几个主要参数需引起我们重视:新增的指令队列延迟Cl(CAS Latency),指在接收列址之后开始传输数据所需时间;接着是行到列的读取指令通道延迟tRCD(RAS to CAS Delay),表示接收行址与列址后开始数据传输所需时间;列重置前的保护tRP(Row Precharge Time),描述了关闭一个行和开启另一个行之间所需的等待时间;以及写入恢复时间tWR(Write Recovery Time)和读出到 predictor 控制器充电周期时间tRTP(Read to Precharge Time),二者对内存读写的操作效率及稳定性具备举足轻重的影响。

读操作时序分析

在DDR3内存的读操作流程中,时序图展示了各信号随时间的演变过程。步骤如下:首先,在接收到读指令后,内存 controller发送出对应的命令信号;随后,经过短暂的等待期,内存 module开始拷贝储存单元中的数据至外部。这整个工序涉及到CL、tRCD、tRP等各项参数,它们紧密协作以确保数据的精准提取及适时传达给CPU。深度解析该读时序图,我们能掌握每阶段所需时间及其各信号间的关联性。

写操作时序分析

如同读操作一样,DDR3内存的写作业同样遵循特定的时序规则。当处理器需将数据输入到内存之中时,内存控制单元便会发出规定的写指令,按照参数tWR及tRP来确定数据传送的确切时刻。数据写入完毕后,为了保证下次操作的顺畅开展,还需要预留余量进行复位操作。通过研究写操作时序图,我们可以精确把握实施各环节所需的时间以及信号间的有机联系。

时钟信号与数据传输

在DDR3时序图中,除 CL 及 tRCD 等关键参数外,还有众多时钟信号如 CK、CKE 等。这些信号统率数据传输节奏与同步方式,直接关乎整个系统运行的稳定度与性能表现。深入分析时序图上时钟信号的定位及其变化走势,将有助于我们精确掌握内存模块与主板间的数据互传机制,为系统调优工作提供科学依据。

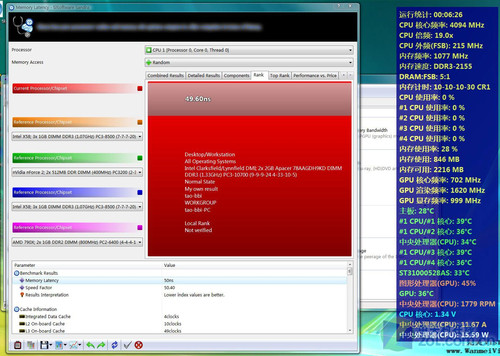

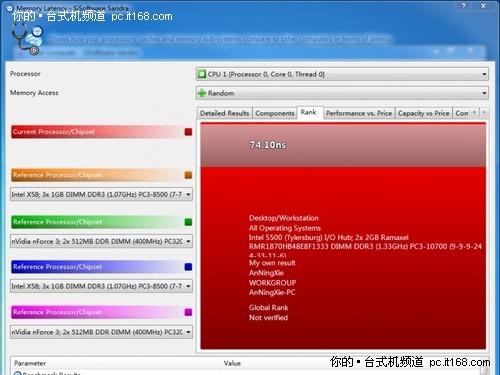

不同频率下的比较

DDR3存储内存不仅具备众多频率选择,而且在特定频率环境下的操作性能亦呈现出不同特征。因此,针对DDR3时序图表进行深入研究时,必须掌握各参数在不同条件下的变动趋势。譬如,在高频设置中,因数据传递更为繁重,对每项参数设定均提出了更高水准;相反,在较低频率状态下,或许会存在部分宽裕空间。经过对各种频率DDR3时序图表的对比研究,便能更全面精确地把握存储模块在各类运行模式中的具体差异。

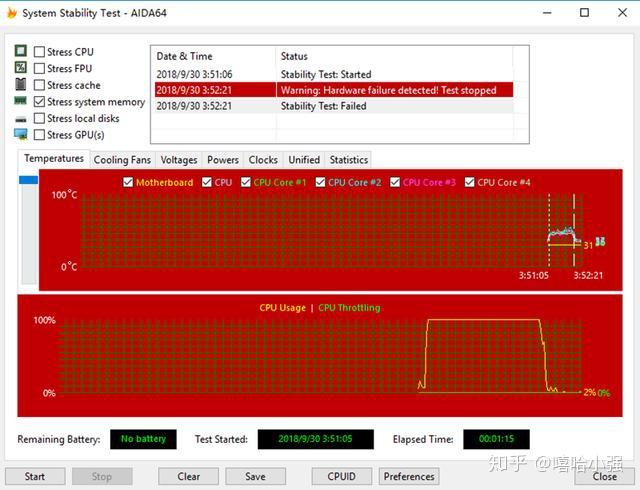

电气特性与稳定性分析

除时间因素以外,DDR3时序图中还涵盖大量的电气特征信息。输出驱动强度、输入电压范围以及噪声容限等项目皆关系到内存模组与主版间信号传输的整体质量与稳定度。借助于此,便可详尽剖析电气特征在时序图中的展露方式,进而评定总体系统稳定性,发掘潜在问题或改善余地。

优化策略与实践应用

通过深度分析DDR3时序图,结合其所存在的瓶颈及缺陷,从而制定相应的优化策略。具体而言,可调整某些参数值,优化布局方式,增强散热效能等措施,以此提升整个系统的性能与稳定度。在实践操作过程中,工程师们会依据DDR3时序图提供的信息进行详细的调试与优化工作,持续改进系统设计以适应日益增长的算力需求。