身为一位专研FPGA领域的专业工程师,我深刻理解DDR3设计在现代众多数字系统中占有举足轻重的地位。本文旨在全面分析和讨论基于FPGA的DDR3设计,覆盖面极广,深入浅出,从前端理论知识到实践运用方法都有所涉及。

1. FPGA技术概述

FPGA,作为一种具有高度灵活性的可重新编程集成电路,因其强大的再配置特性而广泛运用于数字电路设计、信号处理以及通信技术等众多领域。相较于传统ASIC(特定用途集成电路),FPGA的开发周期更短,适应性和成本效益更高。在现今的电子设备中,FPGA发挥着至关重要且无可替代的角色。

随着FPGA设计的深入发展,DDR3作为业界主要的内存类型,高带宽及低能耗的优点使其在数据存储与处理领域得到了广泛应用。而通过精心制定DDR3接口与FPGA间的通信协议以及数据交换策略,便能充分展现DDR3内存的性能潜力,从而有效提升整个系统的运行效能。

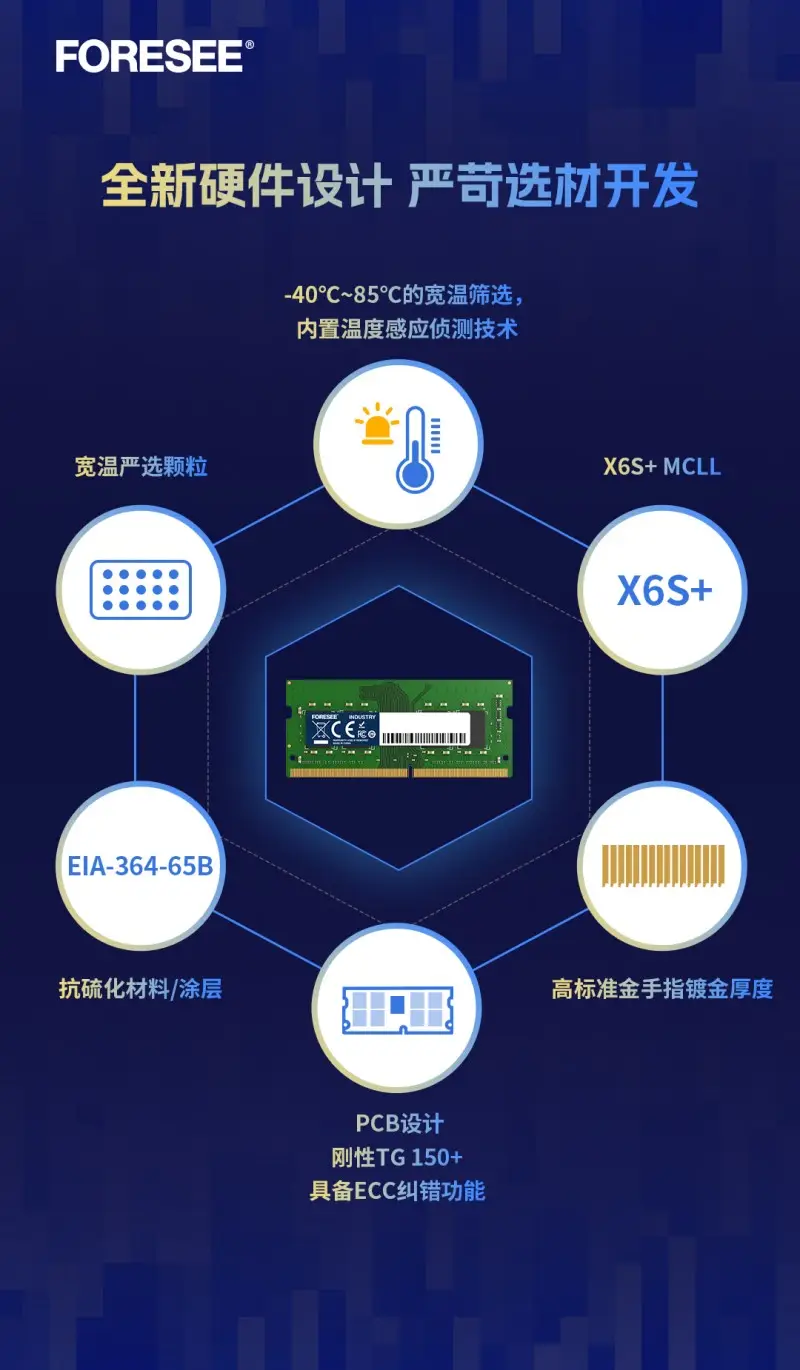

2. DDR3内存技术详解

DDR3内存乃是双倍数据速率的同步动态随机存储器(SDRAM),相较于DDR2存取得更高的带宽与更出色的能源效率。因其高速率、低能耗以及可靠性,DDR3内存现已被广为应用。

在FPGA和DDR3内存连接的过程中,必须充分关注时序限制、电器性能匹配以及接口协议等因素。借助恰当的时钟设定、数据交换模式以及规格化时序参数,能够实现对两系统间稳固无误的数据交互。

3. FPGA DDR3接口设计

实际运用中,构建FPGA与DDR3存储器间的精确接口设计显得至关重要。高质量接口设计可提升系统整体效能,缩短响应时延,以及简化系统调整及保养流程。

于FPGA DDR3接口,其设计包含了物理层接口、逻辑层接口及控制层接口元素,遵循相关标准或规范可实现高效且稳健 FPGA与DDR3内存间通讯。

4.时序约束与布线优化

在FPGA中的DDR3设计阶段,时序约束至关重要。科学制定此约束可保证数据及时准确地传至目标器件,防止时序错误。同时,还需注重布线流程优化,以降低信号传输时延与能耗开支。

考虑到DDR3内存频繁读写特性,应着重注意保持信号传输路径长度与有效差分信号相匹配以优化布线。借助恰当的布线策略以及先进的布线工具,我们得以提升系统整体性能且降低能耗成本。

5.电路仿真与验证

在 FPGA DDR3 设计终了之后,电路仿真和验证显得尤为重要,这是因为此操作有助于尽早识别潜在隐患,实现设计的改进与优化。

在仿真阶段,要充分考虑包括时钟频率、数据传输速率以及信号完整性的因素,必须严谨地对所有可能的场景进行详细验证,以保证系统在任何环境中均可稳定运行且符合预期性能标准。

6.系统集成与调试

在完成电路模拟验证之后,我们需将FPGA DDR3设计整合至综合系统内,开展调试操作。在此过程中,所有模块间的通信协议以及数据交换途径均须深入考量。

在测试过程中,易出现时序及数据传输问题。面对这些挑战需逐层掘出症结,修补完善。通过合理的调试和优化措施,使得整体系统能够平稳且高质量地运转。

7.性能优化与未来展望

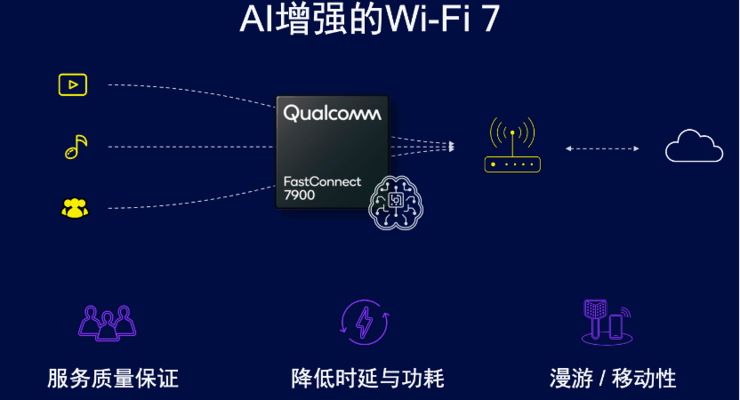

随着科技创新持续演进,FPGA与DDR3协同设计亦须不断完善改进。预期未来DDR4及DDR5等新型存储器技术出现之际,如何妥善运用新技术推进性能优化,将成为重要议题。

追求卓越的过程之中,实际应用尚须考虑功耗优化和安全提升等多个层面。不断研究探索前沿科技,以实际应用为导向进行创新设计,方能精准把握市场脉搏,引领行业迈向更大辉煌。