身为硬件设计师,我深谙DDR(双倍数据速率)技术对现代电子设备的关键性。DDR硬件设计包括内存模组、控制器、时序控制和电源管理等诸多环节,是现代计算机体系中至关重要的组成部分。本文将详细剖析DDR硬件设计的各个层面,从其内部构造至性能优化,引领您共同揭示DDR硬件设计的神秘面纱。

1.DDR硬件设计概述

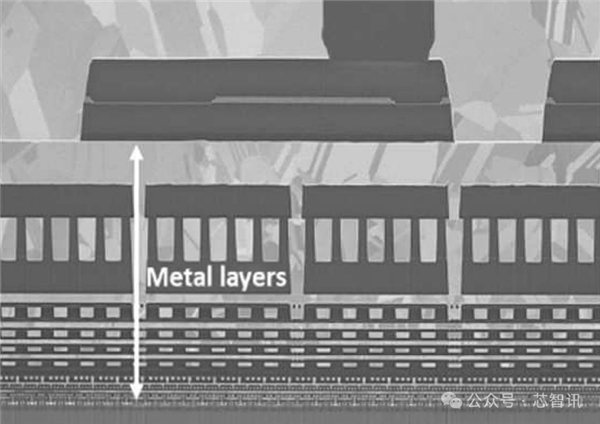

DDR内存技术涉及众多环节,如内存模组、控制器、信号线以及时序电路等。其中,内存模组作为核心部件,承担着数据存储及传输至处理器的任务。DDR内存模组主要由DRAM芯片、PCB板、连接器构成,设计过程中需充分考虑信号完整性、能耗、散热等因素。而DDR控制器则扮演着系统中枢的角色,负责管理内存读写、时序控制、错误检测与纠正等多项功能。在设计DDR控制器时,需注重性能、稳定性及兼容性的平衡,以保证整个系统的稳定运行。

2.DDR内存模块设计

DDR内存模组设计在DDR系统中尤为关键。首要问题在于模组布局与布线直接关乎信号完整性及电气性能表现。合理的布置能有效减少信号干扰及时序差异,从而提升系统稳定性与运行效能。其次,内存模组的PCB设计需综合考量信号线长、层间间距以及能耗分布等因素,保证信号品质与电气性能符合标准。最后,内存模组的散热设计同样不可忽视,尤其在高性能环境下,良好的散热策略可显著增强内存模组的可靠性与使用寿命。

3.DDR控制器设计

DDR控制器作为DDR系统的关键要素,对系统性能及稳定性具有决定性的影响。首要任务在于,DDR控制器需严格执行时序控制,保证内存读写操作的精准度和稳定性。这包括时钟信号产生、延迟调整以及数据校准等多重环节,需充分考虑内存芯片特性和系统运行频率。此外,DDR控制器还需具备错误检测与纠正功能,以提升系统的可靠性和稳定性。此项功能涵盖了ECC编码、数据校验以及错误处理等诸多方面,需从硬件和软件两个层面进行精心设计和优化。

4.DDR信号线设计

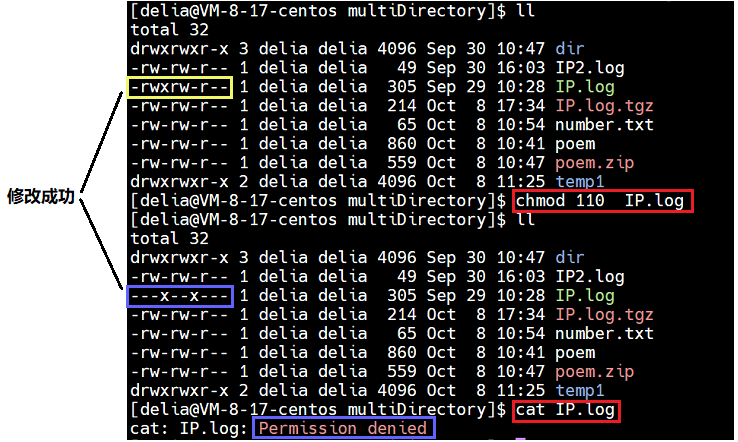

在DDR系统中,信号线设计对系统性能具有关键作用。首要任务在于确保信号线布局符合信号完整性及时间顺序要求,以防信号窜扰与时序偏离,从而提高系统抵御干扰与稳定性。同时,信号线的长度及匹配度亦直接影响着系统性能。过长的信号线将引起传输延时增长,进而影响工作频段与性能。为达到最佳效果,应透过优化布线与信号线长度匹配来提升系统性能。

5.DDR时序电路设计

在DDR系统中,时序电路设计尤为重要,因为其直接关系到整个系统能否稳定运作。该设计需包括时钟信号产生与延迟控制以及数据同步等环节,严格把控时序关系,保证数据传输及处理的准确性。在实际操作过程中,设计师必须充分考虑内存芯片特性、时钟信号稳定性以及数据通路延迟等因素,以确保系统能在预定的时钟频率下正常运行。

6.DDR电源管理设计

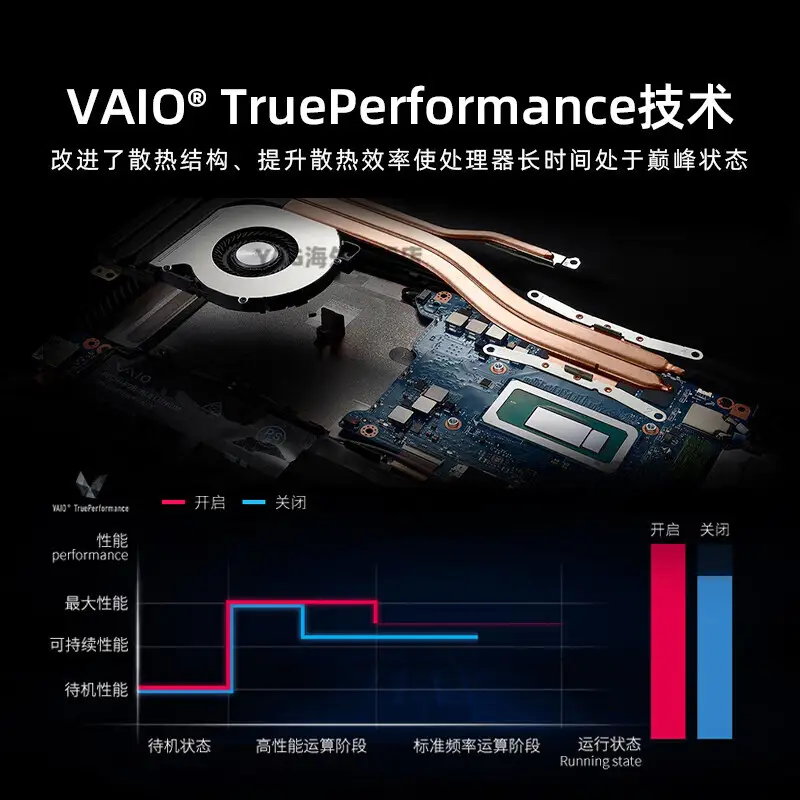

DDR系统中电源管理的合理设计是保证系统稳健运行的关键环节,涵盖了供电电压的稳定、能耗的调控以及温度的管控等诸多领域。面对复杂多变的系统工作情况及环境状况,需要进行全面细致的考量。优良的电源管理设计能有效降低系统能耗、提升系统稳定性,同时也有助于延长设备使用年限。为此,我们必须在硬件与软件两个层面进行精细化的设计与优化,以满足系统对电源管理的高标准需求。

7.DDR性能优化

DDR性能优化作为提升系统性能的重要途径,其内涵包括时序调整、信号线改善以及电源管理的精细化控制等多个层面。此项工作需全面顾及系统硬件与软件特性,方能实现高效、快速的系统操作。