探寻ZynqDDR4的原理,使我备感激动与挑战。身为研究者,我明白到DDR4技术在当代计算机系统中具有举足轻重的地位。而Zynq芯片,这家赛灵思公司的独特组合产品——嵌入式处理器与可编程逻辑器件,其中的DDR4控制与管理显得尤为关键。本文将深入剖析ZynqDDR4的工作原理,从硬件设计至信号传输,逐步揭开其神秘面纱。

1.DDR4概述

首先,让我们对DDR4进行详细的认识。DDR4即双倍数据速率四代,被广泛应用于计算机内存中,它是一款高速动态随机存储设备。与前代相比,DDR4在频率、带宽高度及功耗方面取得了显著进步。其内部构造精细且复杂,需严格的控制和管理。在Zynq芯片中,DDR4作为核心的系统存储器,其性能直接决定了整体系统的运行效率和稳定性。

DDR4主要包含存储单元及控制逻辑两大部分,前者负责数据储存,后者对读写过程实行管理调控。Zynq芯片内嵌有DDR4控制器,通过复杂的控制信号与内存模块进行实时交互,实现高效率的数据传送和保存。

2.Zynq架构

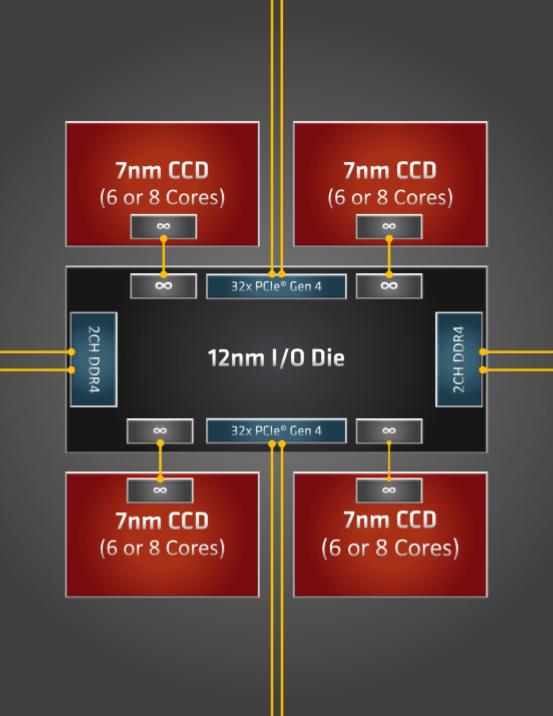

本文将深入解析Zynq芯片的核心结构。Zynq,为赛灵思倾力打造的SoC(SystemonChip),集结了ARM处理器及FPGA可编程逻辑器件两大优势。其独特设计赋予了Zynq卓越的计算性能以及高度的灵活性,广泛适用于嵌入式系统及高性能计算等领域。

Zynq芯片内,DDR4控制单元衔接了处理器系统、可编程逻辑及其他外设,承担着处理处理器与外设对内存读写请求,以及与DDR4存储设备间的数据交互任务。Zynq架构的显著特点是其高度灵活性和可扩展性,为开发者提供了依据应用需求自定义逻辑功能,实现各类复杂系统设计的可能。

3.DDR4控制器

Zynq芯片内的DDR4控制器,作为一个复杂且重要的硬件组件,其职责在于高效地操控DDR4内存的读写运作,以及精确地控制存储设备与处理器系统间的数据传输。此控制器与处理器系统之间,借助高速总线进行紧密连接,从而实现了高效率的数据交互及处理。

DDR4控制器具备地址译码、数据缓存以及时序控制等重要职能。其通过多样化的控制信号与DDR4内存进行高效沟通,从而实现对存储设备的读写操控。此外,该控制器还承担着DDR4内存的初始化及配置工作,以确保系统运行的稳定与性能表现。

4.时序控制

在DDR4芯片的控制机制中,时序控制起着至关重要的作用。为了保障DDR4存储器读写操作过程中的准确性,每个时序信号的产生与同步都需严格遵循标准,任何细小的偏差均可能引起数据传输失误及系统崩溃等问题。为此,DDR4控制器必须对每项时序进行精准把控,以确保数据安全传送与可靠存储。

时序控制包括时钟信号产生、定时参数设定与计时校正等环节。鉴于DDR4存储设备特性及运行环境,DDR4控制器需针对性地调整各时间参数,旨在确保数据传输稳定性与可靠度。同时,该控制器也须实时监控时序信号波形及其对应关系,以便动态修正计时偏差,保障系统运行稳定性在各类环境下均能达到最佳状态。

5.数据传输

除定时控制外,数据交换亦为DDR4控制器另一关键功能。此款存储器具有极高数据传输速度,常达到每秒数千兆字节乃至更高。因此,DDR4控制器需具备高速数据处理能力,确保数据准确无误且无损。

数据传输环节需涵盖数据缓冲、对齐与校验诸多要素。DDR4控制器在读写过程中需妥善处理数据缓冲区,保障数据实时传输及处理。此外,对齐与校验数据亦是其重要职责,旨在确保数据精确度与完整性。此项任务需借助精妙算法与高效硬件设计得以实现。

6.内存管理

相较于常规数据传输与时序掌控,DDR4控制器亦承担着内存管理重任。该项任务涵盖了内存地址映射、内存空间的划定及调整等关键环节。依据处理器系统反馈,DDR4控制器需灵活调控内存空间,确保系统资源得以充分利用。

内存管理须控制地址映象表的运作、模拟页面替换算法及防护机制。DDR4芯片需具备迅速展查内存数的能力,依需求转换物理页面与执行数据保护。此外,如多任务操作系统所需,其还需支持内存管理机制,以实现各进程间的内存隔离与共享。

7.性能优化

最后,探讨下如何提升DDR4控制器的性能。该控制器的表现关乎到整个系统的操作效率及稳定性,故其性能优化尤为关键。

性能优化涵盖了时序调整、数据流速调优以及存储器优化等多项事宜。DDR4控制器的以提升数据传输效率与可靠性为主要目标,主要依赖于对时序参数及数据传输机制算法进行精细化调校。此外,DDR4控制器亦需优化内存管理策略,降低内存访问延迟与冲突,从而提升系统的反应速率与处理能力。

在性能精进过程中,务必连贯权衡系统硬件条件、任务负荷以及性能需求等因素,精确运用合适的数学方法及科技手段开展优化操作。唯有从全局出发,实现深入优化,方能使DDR4控制器展现其最优秀的性能潜能,以满足系统对于高效性与稳定性的严苛要求。