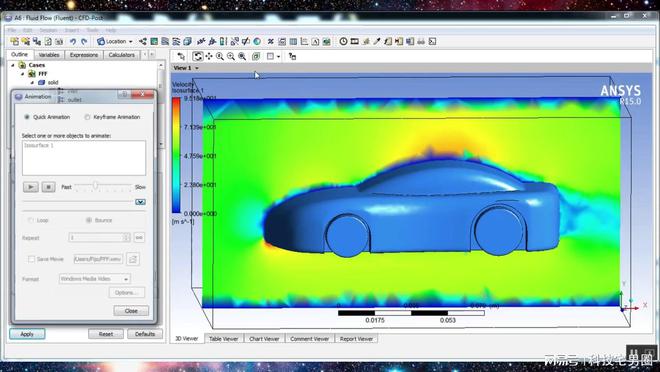

身为资深硬件工程师,DDR仿真是日常工作中的必备步骤,以确保设计的准确性。近期,在执行DDR仿真的过程中,我遭遇了棘手的问题——读出数据出现乱码。这对我的工作造成了极大困扰,因为数据的精确度直接影响到系统的稳定运行。经过深入研究与实践,我成功解决了此问题,现将经验分享如下。

了解DDR仿真

首先,有必要熟悉DDR(DoubleDataRate)技术的基础概念。作为一种具有两倍于传统SDRAM传输速率的内存类型,它显著提升了系统运转效能。在进行DDR仿真的过程中,需关注信号完整性及时序关系等关键要素,以保证数据传输与读取的精确无误。若出现数据乱码现象,则可能源于信号干扰或时序误差等问题。

可能原因分析

在分析数据乱码的问题时,需先排除设计缺陷、信号干扰、能耗问题以及时钟频率设定不当等诸多因素。在进行DDR仿真过程中,务必全面审查系统,以发现潜在的问题所在。

优化布线设计

布线设计对DDR仿真的影响颇大,严谨细致的布局能降低信号串扰与干扰,进而保障信号完整度;若出现数据乱码现象,这正是调整布线设计以优化信号传输质量、降低数据误码率的良好时机。通过调整布线长度、增设地线以及缩小回流环等手段,可显著增强系统稳定性。

解决信号干扰

信号干扰乃造成数据乱码的常见因素,若在DDR仿真期间,因系统中存有此类干扰现象,便可能引发数据传输错误。为了消除信号干扰,可采用多种技术手段,比如加大屏蔽外壳厚度、强化接地线路、缩短信号传输路径等。如此一来,便能显著降低信号干扰程度,从而提升系统运行的稳定性和可靠性。

优化时序关系

时序精确度对DDR仿真的重要性不可忽视,其误差将直接引发读错数据,进而产生数据紊乱问题。因此,进行DDR仿真期间需精细调节时间变量,确保持续正常传输时钟与数据信号。通过优化时序,可显著降低数据误码率,提升整体系统效能。

调整时钟频率

设定适宜的时钟频率对DDR模拟的准确度具有关键性影响。无论是过高还是过低的时钟频率均会引发数据传输偏差以及误码现象。在面对这类问题时,建议尝试调整时钟频率以寻找出最适用于系统运行的频率。适度地调整时钟频率有助于提高数据传输的稳定性并降低数据出错率。

总结经验

深入剖析并成功解决DDR电路仿真中的突发数据错误难题使我深刻领悟到,硬件设计中细微之处至关重要。布线设计、信号干扰以及时序关系等众多因素均能对系统性能产生深远影响。面对此类问题,应沉下心来,仔细分析,找到问题症结所在,进而采取针对性措施予以解决。唯有不断积累经验,方能提升个人技术能力,以更佳状态应对未来挑战。