探索DDR模式解串奥秘的过程中,我被深深地吸引进了这个充满挑战的领域。作为一种内存技术,DDR(双数据速率)解串环节涉及诸多复杂的因素与技术细节。本文将对DDR模式解串的原理、方法及核心问题进行深度解读,期盼能给读者带来启迪。

DDR模式解串的基本原理

先要明确,DDR模式下解串的根本在于,其利用每个时钟周期两次数据传输(即上升沿与下降沿各传送一次)以提升读写速度,故称之为双倍数据率。而解串则旨在把这两次传输的数据变为有效的信号。在这个实际操作中,DDR内存必须在解串过程中处理复杂的时序、电压及干扰问题,以保证数据传输的精确度和稳定性。

DDR模式解串技术的核心理念在于:依据时钟信号的上升与下降边沿,精准且适当地采集数据线上的电压值,进而捕获有效的数字位信息。经过精心的电路设计以及时序调控,我们能保证在每个时钟周期内都能精确地获取所需数据,达成高速、稳定的数据传输效果。

DDR模式解串的方法和技术

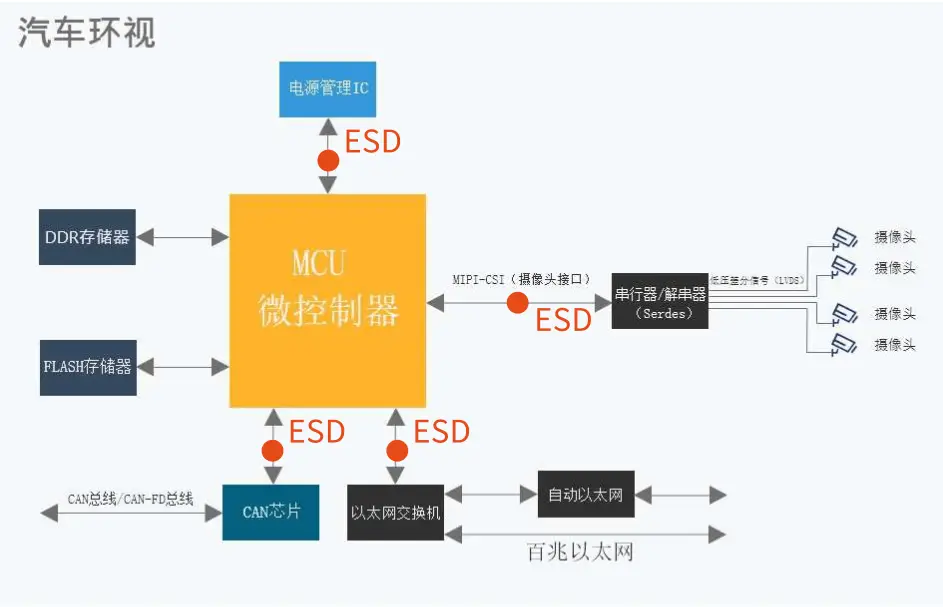

实现DDR模式解码需求诸多工程手法与技术支持,包括电路设计(涉及包括数据线、时钟线及控制线在内的精密布局)、时序调控(为确保数据采样与解析精确无误,每周期均需严格管控)以及对于信号传输延迟、能耗及噪声等问题的充分考量及相应改善措施。

在DDR模式解串处理环节,主要运用了预取、数据校验及错误校正等尖端技术与精确算法。这些先进技术有助于提升数据传输的高效性及可靠性,从而保障系统的稳定运作。同时,借助于如信号分析仪、示波器等辅助设备及工具体系,我们能够更加精准地监控并深入分析数据传输状况,有效发现并迅速应对潜在问题。

DDR模式解串中的关键问题

在实践运用中,DDR模式下解码过程可能面临一些重大挑战,必须加以重视并予以妥善处理。其中之一便是时序匹配问题,即数据传输时的时钟信号与数据信号的延时或偏移可能导致解码失效甚至产生错误。针对这一状况,可通过时钟相位的调整以及布线结构的改良来加以改善。

此外,防止噪声干涉(包括电磁环境及信号间串扰等)同样至关重要,此类问题可能会削弱数据传输的精确度与稳定性。因此,应采用屏蔽技术以及增设冗余校验码等方式以提升系统的抗干扰性能。

除了软件问题之外,部分硬件问题或设计瑕疵也会对DDR模式下的解串性能产生负面影响,例如电路元器件受损、接线失误等。针对此类情况,需进行细致的检查与分析,并采取相应的修复或调整措施,以保障系统的稳定运行。

结语与展望

DDR模式解串作为一项核心技术,对当今的计算机及通信设备至关重要。深刻理解其原理和方法,有助于克服各类难题,提升系统性能与稳定性。面对日益创新的科技,DDR模式解串领域必将迎来更多机遇与挑战。我期待能在此领域持续求知和进步,尽己所能服务于实践问题的解决。