身为硬件发烧友,对于DDR53600时序参数颇感兴趣并充满热情。时序乃内存模块重要指标,直接影响其稳定与性能。尤其是在于DDR53600如此高频率环境中,时序设定显得尤为关键。以下,笔者将针对时序核心原理,详述DDR53600时序深层奥妙。

时序是什么

时序,即内存信号传输的时间次序,对内存稳定性及性能有重要影响。典型的时序参数包含CL(CASLatency)、tRCD、tRP、tRAS等,各自对应特定时间间隔。以DDR53600这一高频为例,其时序设定对硬件稳定程度与制造精度提出了更高要求。

DDR53600频率的内存时序优化,不仅需要权衡各参数间的关系,也不只是单一指标的最优兼顾,尤其是在高频率下,所以时序设置要尽可能细化与审慎。过紧时序可能影响内存稳定性,过松则会对其性能发挥产生影响。因此,调整DDR53600的时序需具备丰富经验及技巧,切勿盲目设定。

DDR53600时序参数解析

在DDR5-3600内存系统中,时序参数主要涵盖了CL、tRCD、tRP及tRAS等方面。CL,即CASlatency,意为列地址解码延时,这直接关乎着内存响应CPU请求的效率;而tRCD则为行地址解码延迟,意味着当内存接收到指令后,其反应时间;对于tRP来说,它代表着行预充电时间,即内存完成关闭当前行并启动下一行所需的时间;最后,tRAS则是行激活时间,用以衡量内存维持开启状态的持续时间。

DDR53600等高频率条件下,时序设定至关紧要。恰当调节这些数值能提高读取及写入效率与稳定性,对系统总体性能产生正面影响。但是,寻求最优时序设定并非易事,需经过反复试验和调整,以及结合具体使用环境,方可得出理想的时序搭配方案。

DDR53600时序调整技巧

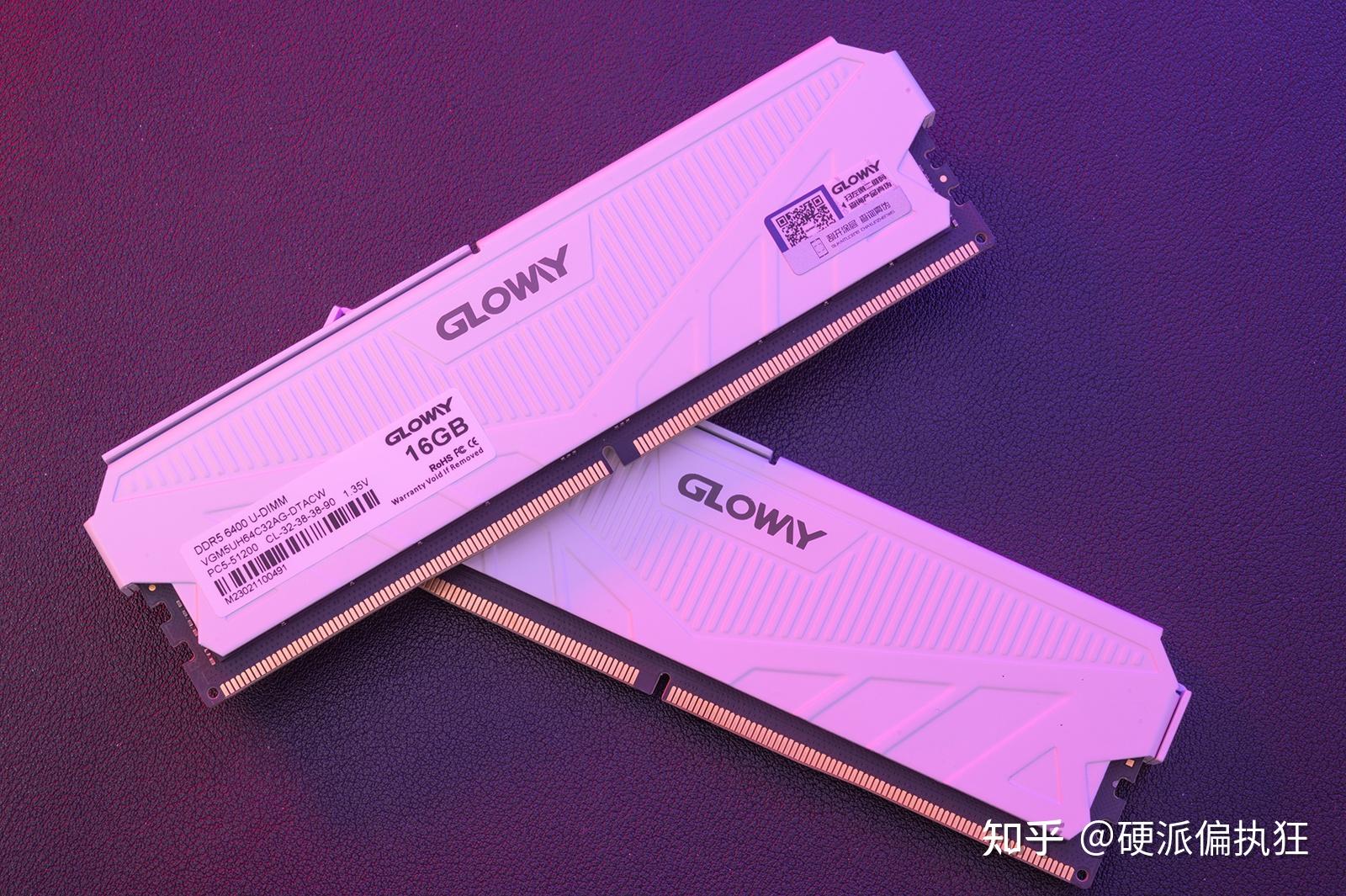

在设定DDR53600的时序时,以下几个方面的建议可供参考。首先,应依据内存颗粒的品质与制造技术来确定适用的时序参数范围。其次,利用超频工具或进入BIOS设置,逐次调整各参数并进行稳定度测试,以找出最优的参数搭配。除此之外,借鉴其他硬件发烧友的经验分享也是获取灵感的有效途径。

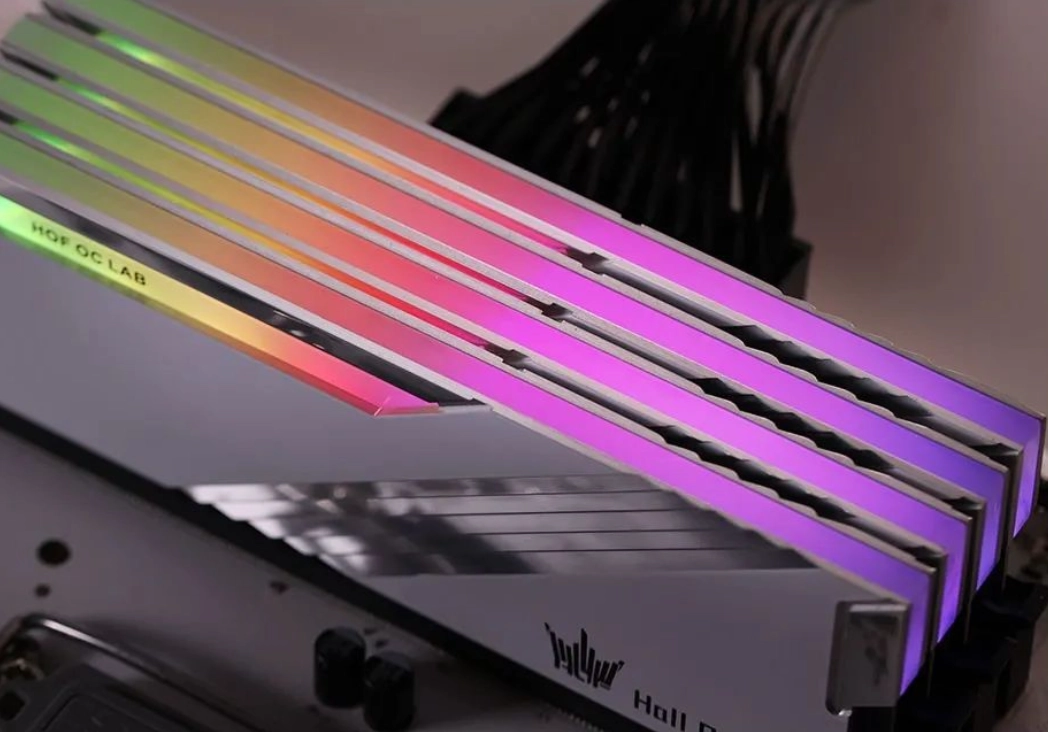

DDR53600调时需慎行,过渡调节恐致硬件损毁且系统失稳。为防范突发状况,建议提前备份重要资料。此外,务必关注内存散热,保证其在高频状态下维持适宜的工作温度,避免高温引发性能降级。

总结与展望

深入研究与探索DDR53600时序调节,既能锻炼挑战精神,亦富有成就感。这些尝试与调整不仅深化了对内存时序理论与影响要素的理解,同时提高了我们自身的硬件调试技术。展望未来,随着科技的持续进步,DDR5内存时序调节将愈发智能化、便捷化,使广大硬件爱好者得以享受DIY的乐趣。

期望通过本文共享,使广大读者对DDR53600时序有更深层次的理解,并提高其实践应用能力。最后,关于DDR53600时序调整方面,欢迎分享您所遇到的独特经历与挑战。