身为电子工程师,深知DDR4校准电路的重要性。随着现代电子设备中DDR4内存普及化,若其稳健及效能未能兼顾,势必影响设备运行。而DDR4校准电路的设计直接关系到内存控制器正确读取和写入数据。故,对该电路原理及其优化策略有深入理解显得尤为关键。

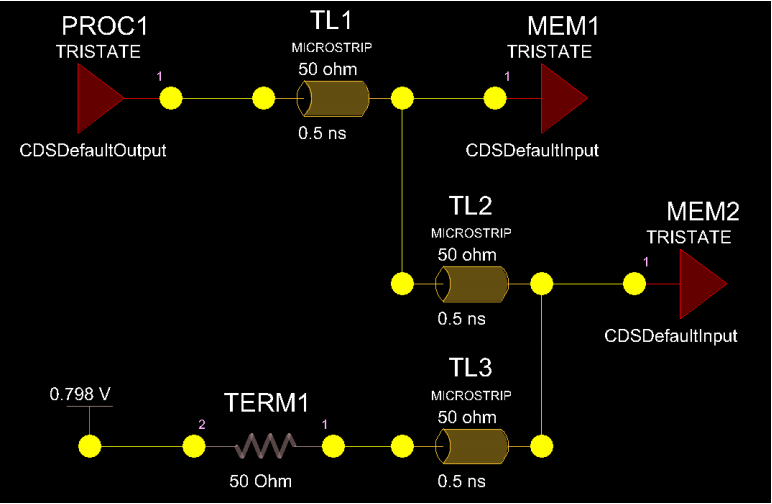

DDR4校准电路包含时钟、数据及地址三项校验,透过此三大校验功能,内存控制芯片能精准识别及定位内存模组内的数据,确保信息传输稳定无误。实际应用过程中,需兼顾时序精确度、电压稳定及信号准确性等因素,以保证校准电路的安全性与稳定性。

DDR4校准电路的设计原理

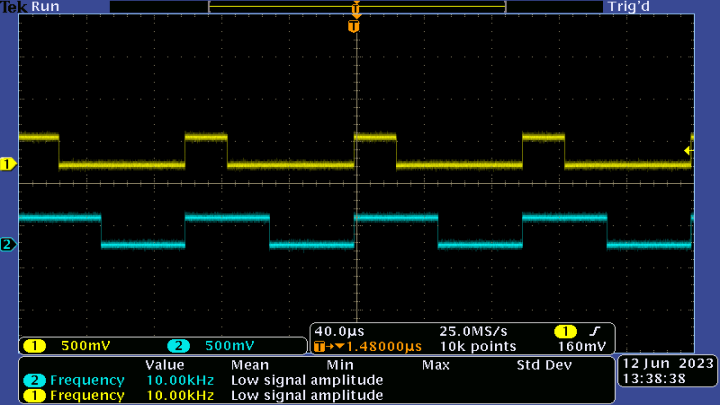

DDR4校准电路的设计原理以及其对时序控制、信号处理及误差校正的综合考量尤为显著。其中,时序控制作为关键环节,主要关注于精准操控时钟信号与确保数据传输同步的需求。值得注意的是,由于DDR4内存所使用的时钟信号频率相较以往更高,故而时序控制的精度直接影响着数据传输的稳定度。

除此之外,DDR4校准模块还需对数据信号进行编码、解码及校验等处理,从而保证信息的准确传达。在这个过程中,误差校正尤为关键,可借助纠错码与奇偶校验等方法,有效侦测并修正数据传递过程中所出现的失误,进一步提升数据传输的稳定性。

DDR4校准电路的优化方法

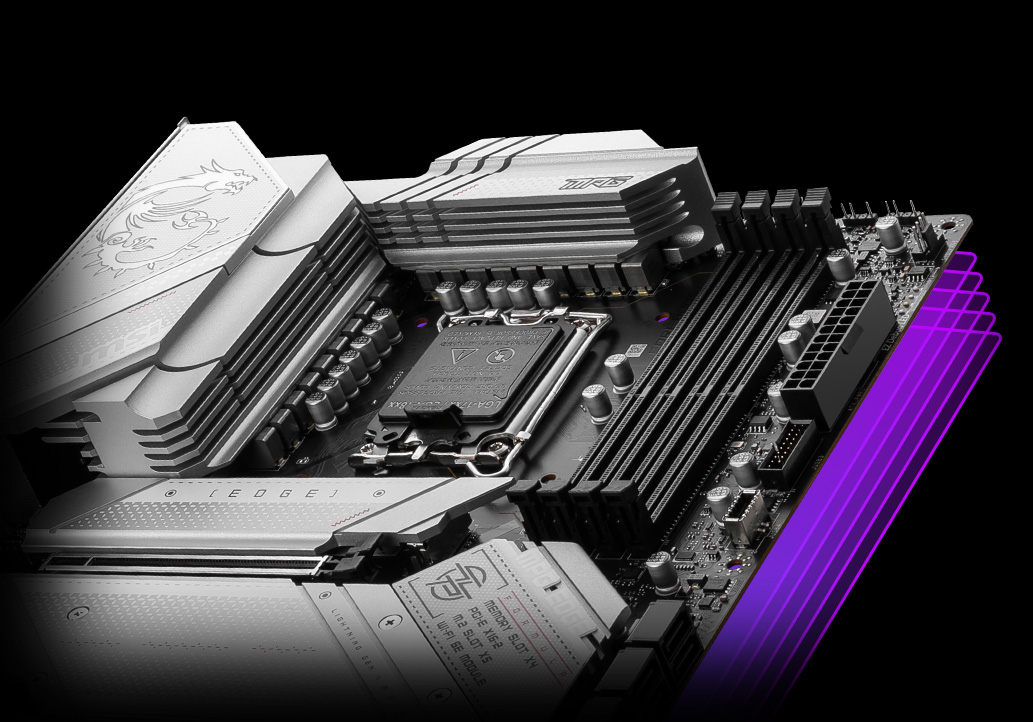

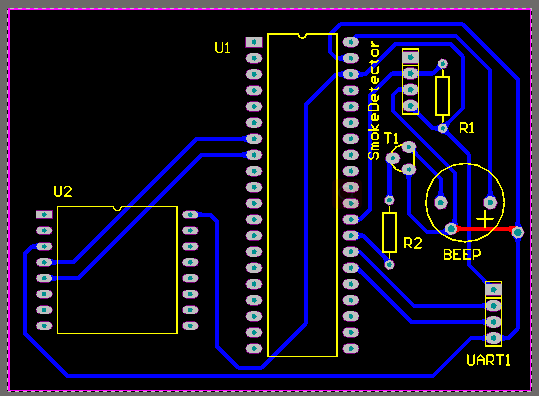

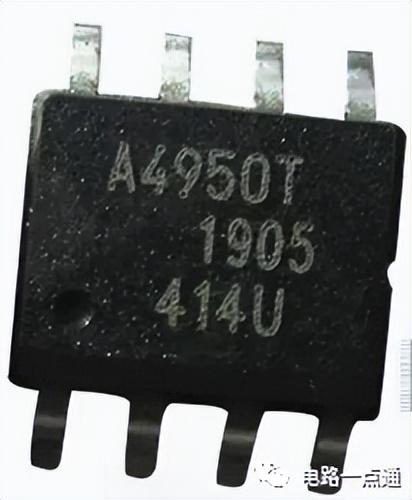

在研发DDR4校准电路时,优化电路构造及提高校准精准度与稳定性成为关键。其中,使用尖端的校准算法并将软硬结合,能显著提升校准精确度及效能。此外,完善供电系统、减少电磁干扰、增强信号完整性的措施也是提升DDR4校准电路性能的有效途径。

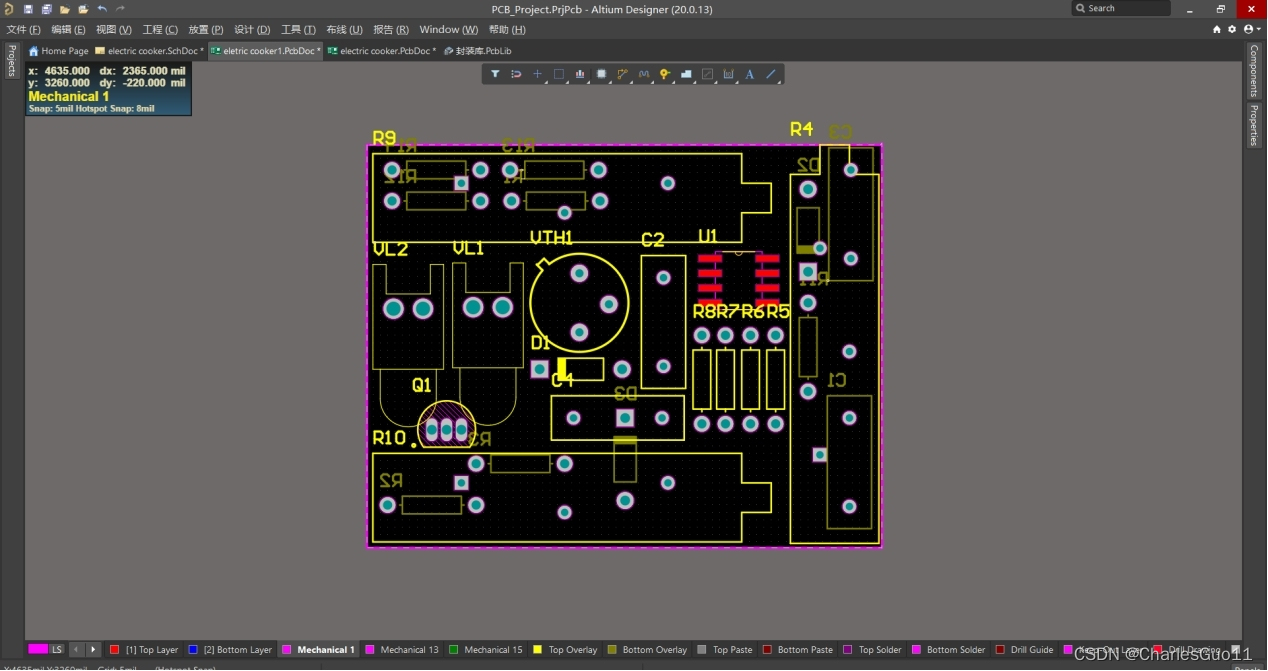

此外,适度设定PCB排布、精炼信号传输途径以及减缓延迟与消耗也都是优化DDR4调谐电路的关键策略。精细策划并优效处理后,我们便能提升DDR4存储模块的稳定性,增强其性能,进而保障数据传输过程中的精准度及可靠性。

DDR4校准电路的未来发展

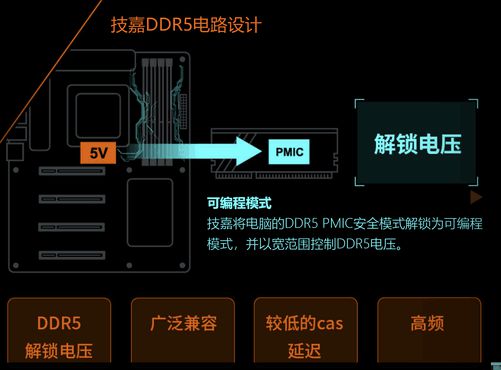

伴随着科技日益精进,DDR4校准电路亦步步更新迭代。展望未来,其智能化趋势与自适应能力必将凸显,环境与工作状况的变化皆可自如应对,系统稳定性与性能双收。同时,DDR5内存之广泛应用,为DDR4校准电路带来新的机遇与课题,唯有持续革新与优化,方能满足新世代内存的需求。

随着技术进步,DDR4校准电路有望实现更快的数据传输速度、更低的能耗以及更强的抗干扰性,从而极大地提高电子设备的性能与节能效果。面对未来,我们充满信心并将持续探索创新,坚信DDR4校准电路的前景将会更加广阔。