身为一名工程师,深知参考时钟对于设计及调试DDR模块的关键性作用。其稳定性与精准度直接关乎DDR模块的表现与可靠性。故而在日常工作中,对于参考时钟向DDR模块提供一事,投入深度的研究与实践,并积累部分经验与感悟。以下,将分享个人对此问题的理解与认识。

1.时钟源选择

选择DDR参考时钟应优先考虑其稳定性与精确度。建议采用稳定度较高的晶振或TCXO作为DDR参考时钟。同时,需关注时钟源频率是否满足DDR需求及输出电平是否符合DDR芯片输入规格。

实战中,我曾面临因时钟源选用不当致使DDR模块稳定性受损的困境。通过深入剖析与反复调试,我们成功锁定了适宜的时钟源,并对时钟信号实施了恰当的电平转换,从而有效地解决了频率波动的问题。

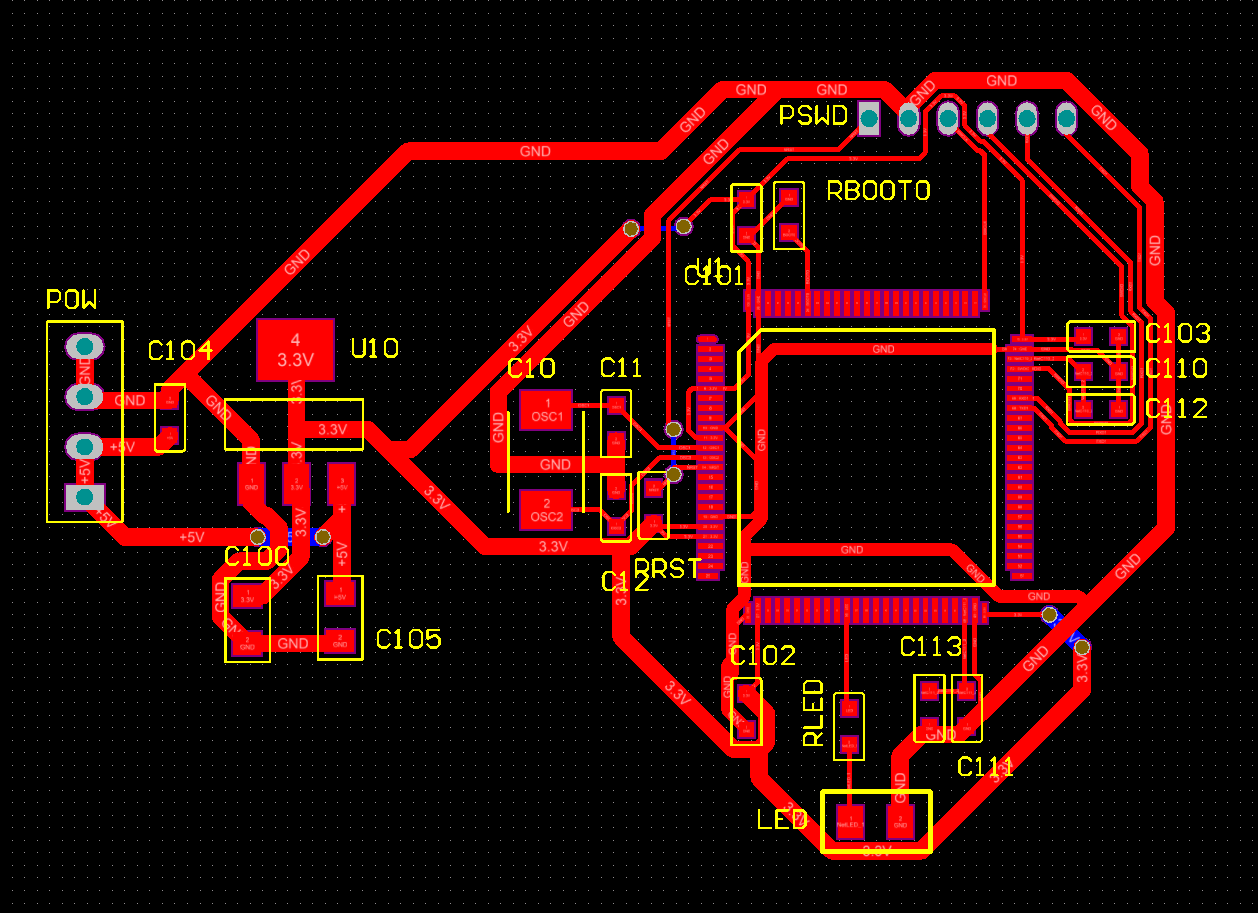

2.时钟布线与阻抗匹配

在选择适当的时钟源之外,DDR模块性能还受时钟信号敷设及阻抗匹配影响。线路设计应尽可能短直以减小信号路径长度与干扰,保障时钟信号稳定传输。此外,需关注时钟信号的阻抗匹配,防止反射与干扰对其传输造成影响,从而保证DDR模块的正常运行。

在之前的项目过程中,由于时钟信号布局欠妥及阻抗不匹配,导致DDR模块无法顺利启动,经过时钟信号布局与阻抗匹配的优化改造后,成功解决问题并提升了整个系统的稳定性与可靠性。

3.时钟信号的同步与延迟

设计DDR模块时,时钟信号的同步与延误问题是关键考量因素。因DDR芯片与时钟源间可能存在相位差异,故需借助同步电路及延迟线以调节信号相位,确保时钟信号同步且稳定运行。

曾在前述项目中,因时钟信号同步失准引发数据传输出错。经精调同步电路与延迟线后,成功解决误差并提升了系统性能。

4.时钟信号的干扰和抑制

除上述问题外,时钟信号的干扰及抑制亦是不容忽视。DDR模块设计过程中,时钟信号极易受其他信号干扰,从而引发波形失真与抖动,对其正常运行产生负面影响。

过去的项目经验揭示,时钟信号的干扰会引发DDR模块频率大幅波动。我以抑制与滤波时钟信号的方式成功解决这一问题,从而提升了DDR模块的运行稳定性。

5.时钟信号的监测与调试

在DDR模块的设计及调试环节,时钟信号的严密监控与调整至关重要。借助示波器、逻辑分析仪等专业设备,我们能精确地观察到时钟信号的状态,找出潜在问题,并实施相应的优化措施。

过去,我曾频繁运用示波器洞察时钟信号并加以深入分析。透过时钟信号的波动与频谱,我们可迅速辨识其是否运作正常。若发现问题,我会立即调整时钟信号的设定与电路设计,以确保DDR模块始终保持良好状态。

6.时钟源的热稳定性和漂移

时钟源热稳定及漂移问题不容忽视。高温或温度波动大的条件易使时钟频率与相位产生漂移,进而影响到DDR模块的运行效果和可靠性。为保障DDR模块的顺利运作,优先选用具备优良热稳定性的时钟源显得尤为关键。

在过去的项目操作过程中,我们遇到了由于时钟源不稳定而导致高温环境中的DDR模块频率异常波动的问题。通过精心挑选具有较高热稳定性的时钟源以及合理地设计散热系统,成功地解决了这一困境,从而提升了DDR模块的运行性能和可靠性。

7.时钟信号的功耗和电磁兼容

最终,时钟信号在功耗和电磁兼容方面亦须审慎考量。其功耗将对系统整体能耗及稳定性构成影响;同时,时钟信号的辐射与抗干扰性能直接关乎系统的电磁兼容性。

往从前的研究项目中,我便已成功实现功耗优化及电磁兼容性的测试,从而提升了整个系统的表现与稳定性。经过精密调整时钟信号功率分配与布线方式,并添加适当滤波器和隔绝技术,最终使得DDR模块在复杂的电磁环境下也能保持稳固运行。

为DDR模组选取适宜的参考时钟颇具挑战性且极其关键,需全盘兼顾诸多要素并经过检验确认。唯有经由持续实践与总结,方能累积丰富经验,提升DDR模组设计的精准度及稳定性。