在如今的电子技术环境下,DDR4内存已普及且被视为主导者。解析DDR4信号流向图对于设计及优化电路具有关键作用。这是因为DDR4信号流向图详细描绘了内存模组上各信号的传输途径与衔接模式。透过对信号走向的深入了解,我们能更直观地理解数据在内存内部的储存和交换进程。

DDR4内存模组内包含诸多繁复线路,用于传输各式各样的信号,如数据信号、时钟信号和控制信号等。认识并领悟DDR4信号走向图能够让我们更为深入理解其工作原理,进而改善电路设计,提升数据传输速率。

数据信号的传输路径

DDR4内存中的数据信号占有举足轻重的地位,负载着实际的数据信息。在DDR4信号流向图中,数据信号的传递路径常常是其中最为繁复且至关重要的环节之一。此信号需经历数据线、数据掩膜、数据缓存等众多元件,方能抵达存储单元,实现数据的读写动作。

在规划数据信号传输路径时,需综合考量其稳定与速率两大关键要素。科学的布线及信号处理方法能缩小传输误差,降低延迟,从而提升内存效率与可靠性。

时钟信号的引入与同步

DDR4内存在内部重要功能之一即为同步及控制时钟信号,其指引数据信号何时可进行读写操作。在信号流程图中,时钟信号需适应数据信号的传输需求以保证数据的同步性和稳定性。

在采用时钟信号的设计中,需充分考量其频率及相位,如此可提升内存效能与稳定性。更为重要的是,在DDR4内存设计过程中,要重视时钟信号的同步性问题,实现时钟和数据的精确同步,方能保证内存长期稳定运行。

控制信号的作用与传输

在DDR4架构中,控制信号起到了精密的控制与指引作用,负责指导数据信号及时钟信号的正常运行。在DDR4信号流向结构方面,控制信号的传输路径需保障其能精准无误地抵达各组件,以确保内存设备的稳定运转。

在设计控制信号时需思考其逻辑关系和传送方式等元素,恰当的设计可提升内存反应和稳定性能。此信号还需与数据及时钟信号整合运作,以确保各部分能协同工作,进而实现高效率的数据处理和传输。

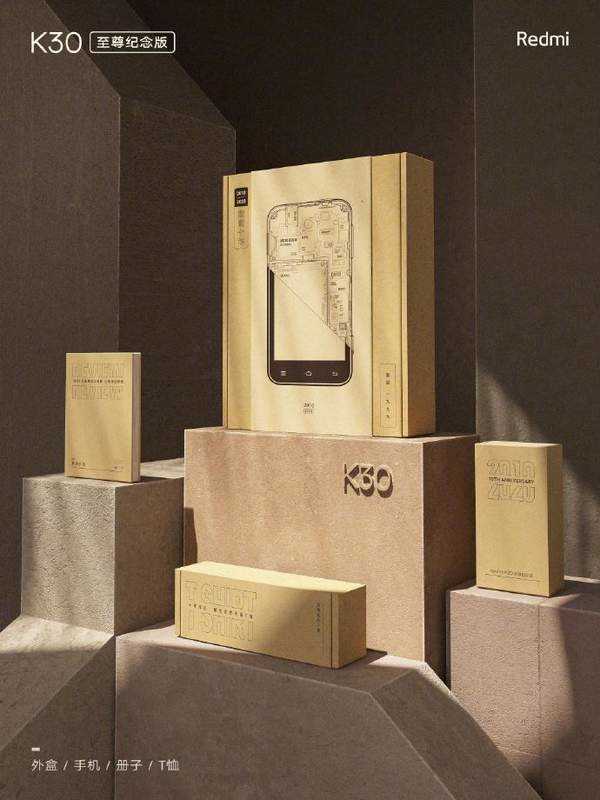

内存模块的布局与信号传输

DDR4内存模块布局直接关乎信号传输效率,而恰当的布局可缩短传输路径,降低干扰,提升内存性能与稳定性。在其信号流程图中,布局需兼顾数据线、时钟线及控制线等各类信号的传输路线,以实现高效且稳定的数据传递。

在此基础上,内存模块的布设亦需慎重考虑信号线间的相互干扰及耦合,以免因外力影响导致数据遗失乃至误解。优质的内存模块布设能有效提升其抗扰性,从而稳定可靠地保证数据传输。

信号流向图的优化与调整

DDR4内存设计的关键环节在于信号流向图的精细优化与调整。这有助于提升内存效能,稳定数据传输并降低延迟与误差。

在优化信号流向图时,需综合考量信号线路布置、长度匹配以及信号处理电路等多重因素。经过适当优化,可显著提升内存在数据传输速率及稳定性上的表现。落地实际应用中,结合实际需求对信号流向图进行灵活调节,亦是DDR4内存设计环节中的关键所在。

结合实际案例进行分析

解析现实案例,深度解读DDR4信号流向及优化策略。研究各类内存模组的信号流向图,能直接明了地了解信号传输路径与连结方式,进而深化对DDR4内存运作机制的理解。

以实例剖析各内存供应商间内存模块信号流程结构及设计差异,揭示其对内存效能的具体影响,旨在指导我们在实际环境下挑选最适宜的模块,优化并调整系统配置,从而提升全面性能与稳定度。

未来DDR4内存发展趋势展望

伴随着科技进步,DDR4内存作为当前主流配置之一,也持续实现着自我更新与完善。展望未来,其发展趋势或许将更加专注于提速、节能、抗扰等关键性能的提高上,以应对日渐增长的数据处理需求。

在将来的DDR4内存研发中,我们有望看到新型信号传输机制及全新结构设计的应用,创造出更快且更为稳定的内存解决方案。与此同时,应考虑到人工智能与物联网等新科技的崛起所带来的对DDR4内存的应用转变及性能需求的改变。为此,我们需时刻洞察其发展动态,持续优化与提升内存设计水平。