作为一名热衷于计算机硬件研究的工程师,我对深入探索PCIe读取DDR内存的运作过程颇感兴趣。在我们生活的这个快速变化的科技时代,计算机硬件技术日新月异,而PCIe接口和DDR内存正是现代计算平台的关键组成部分。深入研究PCIe读取DDR内存的流程,不仅能让我更深入地理解计算机系统的工作原理,也能激发我未来职业生涯中的创新思维。

PCIE接口简介

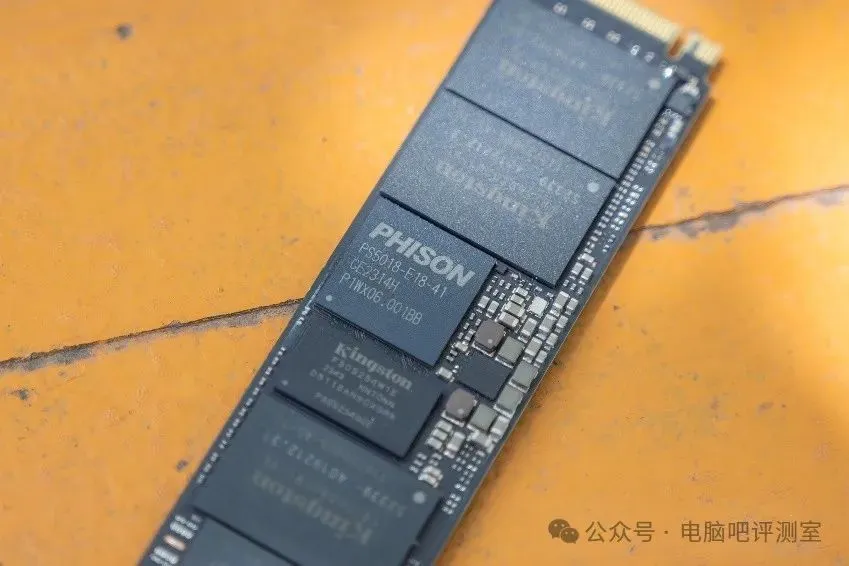

PCIExpress,简称PCIe,是专为实现主板与各类外围设备(例如显卡、网卡和固态硬盘等)快速数据传输而研发的高速串行接口。其卓越的性能显著提高了计算机的运行效率和处理能力,已然成为现代计算机体系结构中不可或缺的一环。PCIe采用差分信号技术进行信息传输,具有极高的带宽、极短的延迟以及支持热插拔的特性,因此被广泛应用于各种设备之间的互联互通。

在PCIE界面内,数据传递以数据包裹为载体实现。包裹内含控制指令以及相关地址和数据信息,经由PCIE总线发送至指定设备。为确保数据安全与稳定,PCIE采用多组通道与虚拟通道对数据包裹进行管理及操作。深入探究PCIE接口运行原理及其数据传输方式,有助于全面理解其与DDR读写过程的关系。

DDR内存介绍

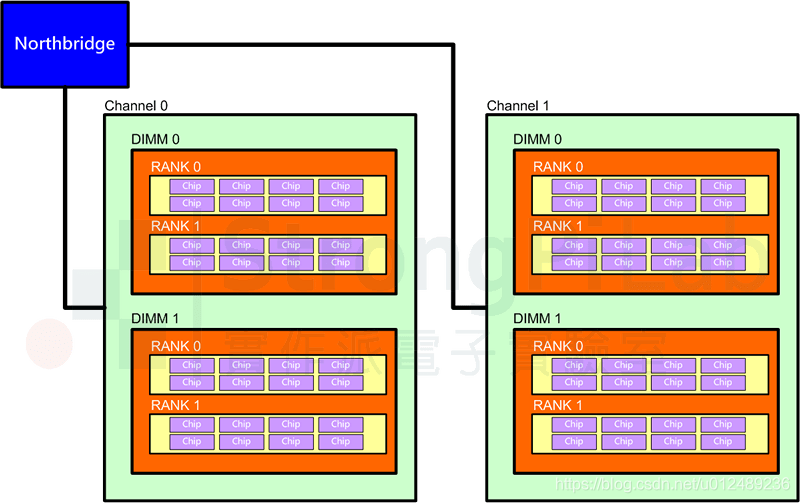

DDR(双倍速率传输)是基本的计算机内存类别,承担存储和传输计算机操作所需信息和应用软件的责任。凭借高速读写性能、节能特性和出色稳定性,它被广泛应用于多样的计算机体系结构中。借助内存控制器,DDR内存能与中央处理器进行高效数据交换,其核心价值在于为数据和程式提供存储服务。

在电脑系统运营中,DDR内存是频繁进行读写操作的关键之一。当CPU需要从内存读取数据时,便会通过内存控制器下达读取指令,DDR内存随即精准提取并传输所需数据至处理器;若是CPU想要往内存写入数据,同样会指示DDR内存将信息精确地存储于指定位置。深入把握DDR内存的读写运作机制和流程,对我们更全方位理解PCIE与DDR之间的读写行为至关重要。

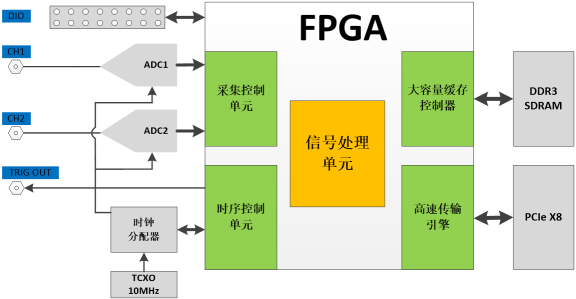

PCIE读DDR流程

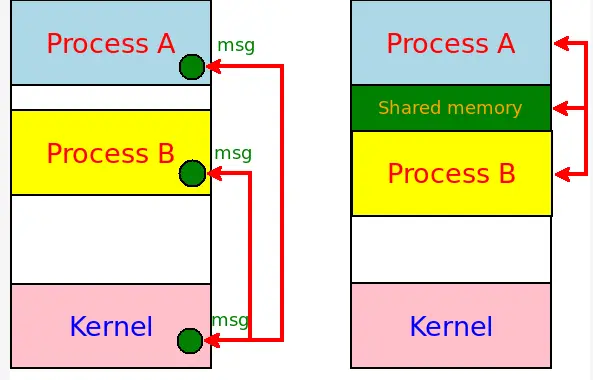

PCIe读取DDR流程即通过运用PCIe接口来完成对DDR内存中的数据读取任务。首先,处理器需发送读取请求给PCIe控制器,确定欲读取数据所在的具体DDR内存地址。随后,接到请求的PCIe控制器会将其转换成数据包,并通过PCIe通道传递到目标设备(即DDR内存)上,以确保顺利完成数据的读取工作。

在DDR内存接收到数据包后,它会根据其中的地址信息提取所需数据,再以数据包形式还给PCIE控制器。在此过程中,PCIE控制器负责接收和解析数据包,随后将其传递至处理器,由处理器将数据写入相应的寄存器或缓存区。显然,这一切都需要PCIE控制器、PCIE总线以及DDR内存之间的密切合作与精确配合,才能确保数据的高效传输与处理。

PCIE写DDR流程

借助于PCIe接口,实现了将数据准确无误地写入DDR内存的操作。此过程与读操作有相似之处,但首先需向PCEI控制器下达写命令以指定所要储存的数据和对应内存地址。随后,PCEI控制器将写出的请求格式化成信息包,并利用PCIe总线将其传输到相应的DDR内存中。

当接收到写入请求时,DDR内存有责任将数据包中的详细内容转化为相应的内存地址并生成应答数据包,随后,这个应答数据包将被送到PCIE控制器。接收此响应数据包的PCIE控制器会进行核实,如果数据写入无误,它就会向处理器发送信号表示任务已经顺利完成。在此过程中,PCIE控制器、PCIE总线和DDR内存之间的协同工作至关重要,以确保数据的准确性和高效处理。

PCIE读写DDR流程图

通过深入探讨PCIe读取DDR的流程及其相关机制,结合流程图视觉表现,可以更直观地理解它们之间的相互作用关系以及数据包在不同模块间的流动路径和方向。详尽分析该图能够使我们更加精准地掌握PCIe读取DDR的运行机理以及流程结构,对于未来系统设计和性能提升具有重要参考价值。

总结与展望

通过对PCIE与DDR读写机制的深度剖析,不仅增进了对计算机体系结构的领悟,更引发了关于硬件设计与优化的深层思索。作为电脑系统内核至关重要环节,PCIE及其与DDR之间高效、稳定的信息交互,对性能提升与使用者感受影响深远。展望未来,期望在这两大关键技术层面继续深耕细作,为推动计算机系统发展献上微薄之力。

对PCIE与DDR交互过程的深入探索,使我累积了丰富知识,深化了对计算机硬件技术的认识和追求。期望通过不断学习和实践,在该领域有所建树,为推动科技进步和社会发展贡献力量。