自步入FPGA领域以来,Xilinx系列产品成为我的得力助手。面对挑战与创新并存的环境,DDR3内存的集成与管理显得至关重要。本文将分享我在运用XilinxFPGA配置及管理DDR3内存方面的心得体会。

初识XilinxFPGA与DDR3

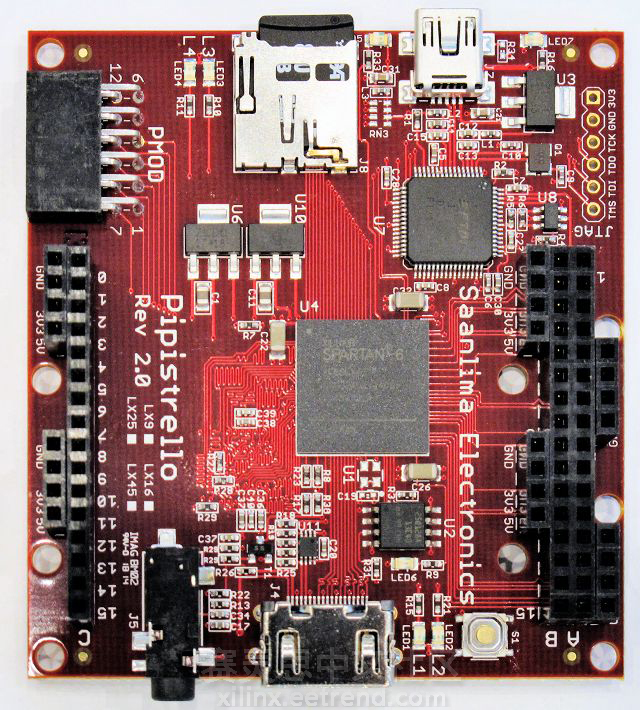

初涉FPGA领域之际,Xilinx这一品牌便深入人心。其所具备的高效性与可靠性,以及先进的技术创新能力,广受赞誉。此外,DDR3内存技术以其高速数据传输能力,被视为项目顺利实施的关键因素。首次尝试将DDR3与FPGA相融合时,面对未知的挑战,紧张与期待并存,那份兴奋之情至今仍难以忘怀。

在掌握硬件知识及深入理解信号完整性和时序约束后,我将FPGA与DDR3技术相结合并付诸实践。虽然每一次细微的失误都可能引发整体系统故障,但每次成功的调试无疑加深了我对FPGA独特魅力的认识。

设计与实现:FPGA上的DDR3控制器

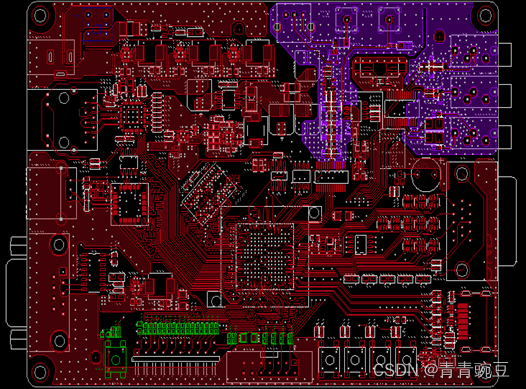

在FPGA上实施DDR3控制器可谓挑战重重。首先,利用Xilinx所供的集成IP核能大大简化此任务,使其重点更加突出于系统总体设计。尽管如此,精确无误地完成每个步骤仍至关重要。

深入研究各参数及配置对DDR3运行效果与稳定性能的影响,包括时钟频率、数据宽度以及校验模式等细节,可谓耗费巨大心血。在历经无数次尝试与修正后,成功掌握了相关配置方法。首次见证DDR3与FPGA顺畅传输数据的那刻,内心的满足感难以言表。

调试过程中的挑战

在FPGA和DDR3项目的调试环节,难度颇大。曾遇到过系统在测试阶段突发随机错误,排查之困令我对硬件产生疑虑,然而经详细核查,硬件并无损坏。继而转向软件配置,逐行代码审视后,终于在一处微小参数设定上发现症结。

此次实践使我深思熟虑:FPGA与DDR3相结合时,精准操控决定成败;小误差足以毁掉整个项目。调试期间,沉着冷静与专注细心至关重要。

性能优化:提升系统效能

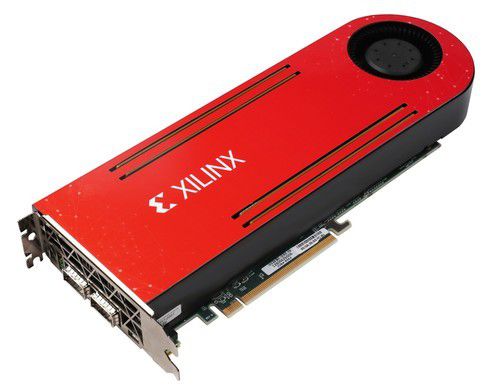

随着项目深度推进,我着眼于提升系统性能,而其中DDR3的带宽及延迟对总体性能至关重要。通过精炼FPGA逻辑设计、优化内存访问方式,从而显著提速数据处理流程,提高运行效率。

在此过程中,我掌握了诸多尖端技能,如运用流水线技术以降低延迟,以及充分发挥双数据速率(DDR)的潜能以拓宽带宽。每次性能的提升都深化了我对FPGA设计的理解,同时也坚定了我对科技探索的决心。

实战案例:从理论到实践

虽然理论知识不可或缺,但若缺乏实践经验,则终究只是空洞的理论。以我亲身经历的视频处理项目为例,其亮点在于必须在FPGA上完成高速视频流的处理任务,而此过程对DDR3的带宽与延迟提出了严苛的挑战。

经过不懈努力和技术优化,我们成功实现每秒处理上亿像素的目标。在这期间,我对DDR3有了更深层次的认知,同时深感理论与实际操作相结合的必要性。

未来展望:FPGA与DDR3的发展趋势

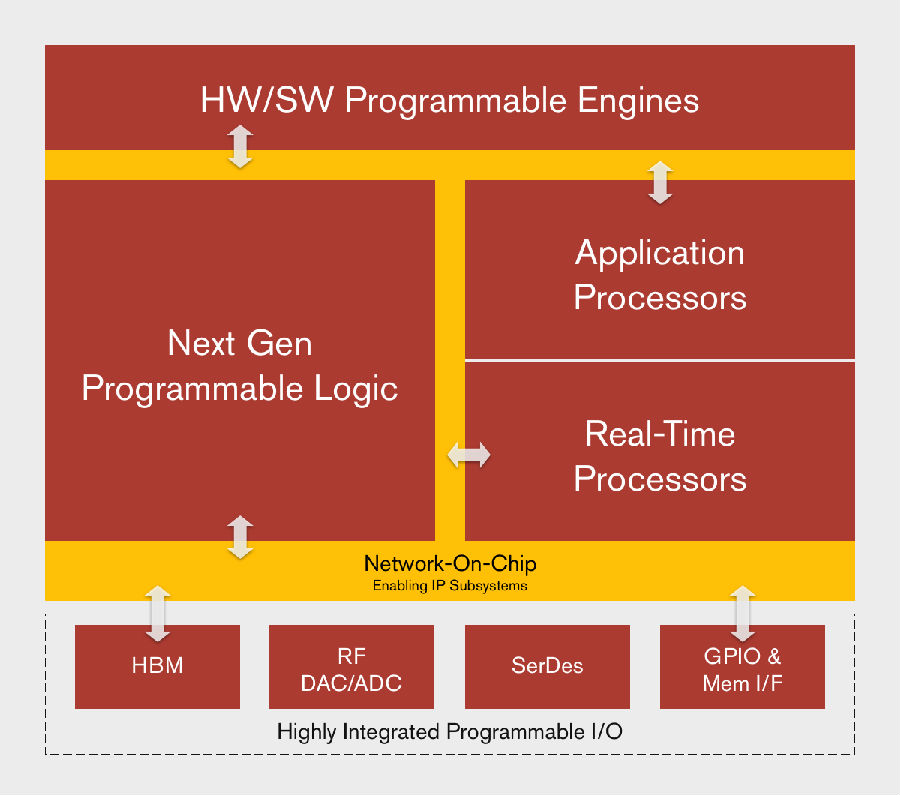

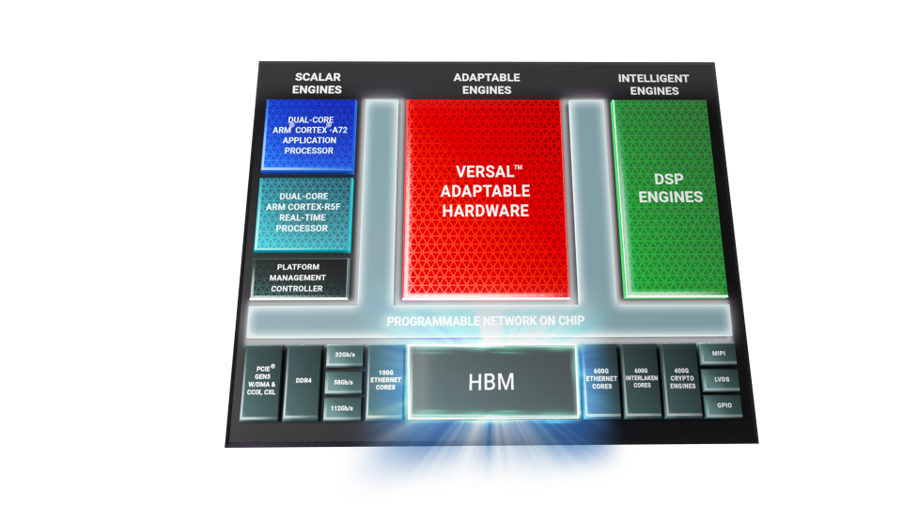

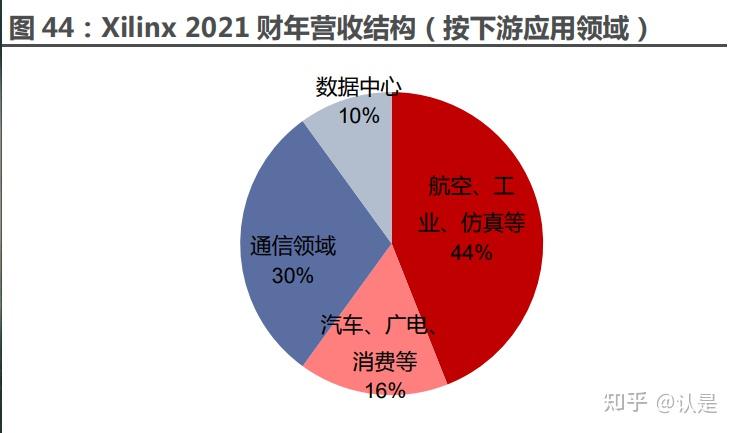

随着FPGA和DDR3内存技术的飞速发展及进步,我们对未来充满信心。随着诸如DDR4、DDR5等新型内存技术的广泛应用,以及FPGA在人工智能、大数据领域的深度运用,我们有理由坚信,未来FPGA与DDR3的结合将会释放巨大潜能。

身为钟爱技术之人,我始终热衷于此领域的深入研究与探索。每一次科技的飞跃,都使我对未来充满无尽的期许。

总结与展望

总结我对FPGA与DDR3的研究历程,我深感骄傲且满意。在这段征程中,尽管遇到诸多困阻,但我也取得众多重大突破。我坚信,随着科技的持续发展,FPGA及DDR3的应用领域将日益扩大,并在未来科技发展中发挥关键作用。

在此,恳请各位分享一下FPGA与DDR3技术项目中所遇到的复杂难题以及有效解决方案,期望能从您的经验中获得启发。诚邀广大读者在评论区踊跃讨论,并请您积极分享此文以便让更多人受益于FPGA与DDR3技术的魅力。