身为电子工程专家,每日需与众多电路原理图相伴,而DDR芯片电路原理图更令我激动且心生敬畏。这犹如探险者于未知海域探索,充满神秘感令人振奋,同时也伴随着潜在挑战带来的压力。今日,愿与诸位共享此感悟,共同深入探讨DDR芯片电路之奥秘。

DDR芯片的基本概念

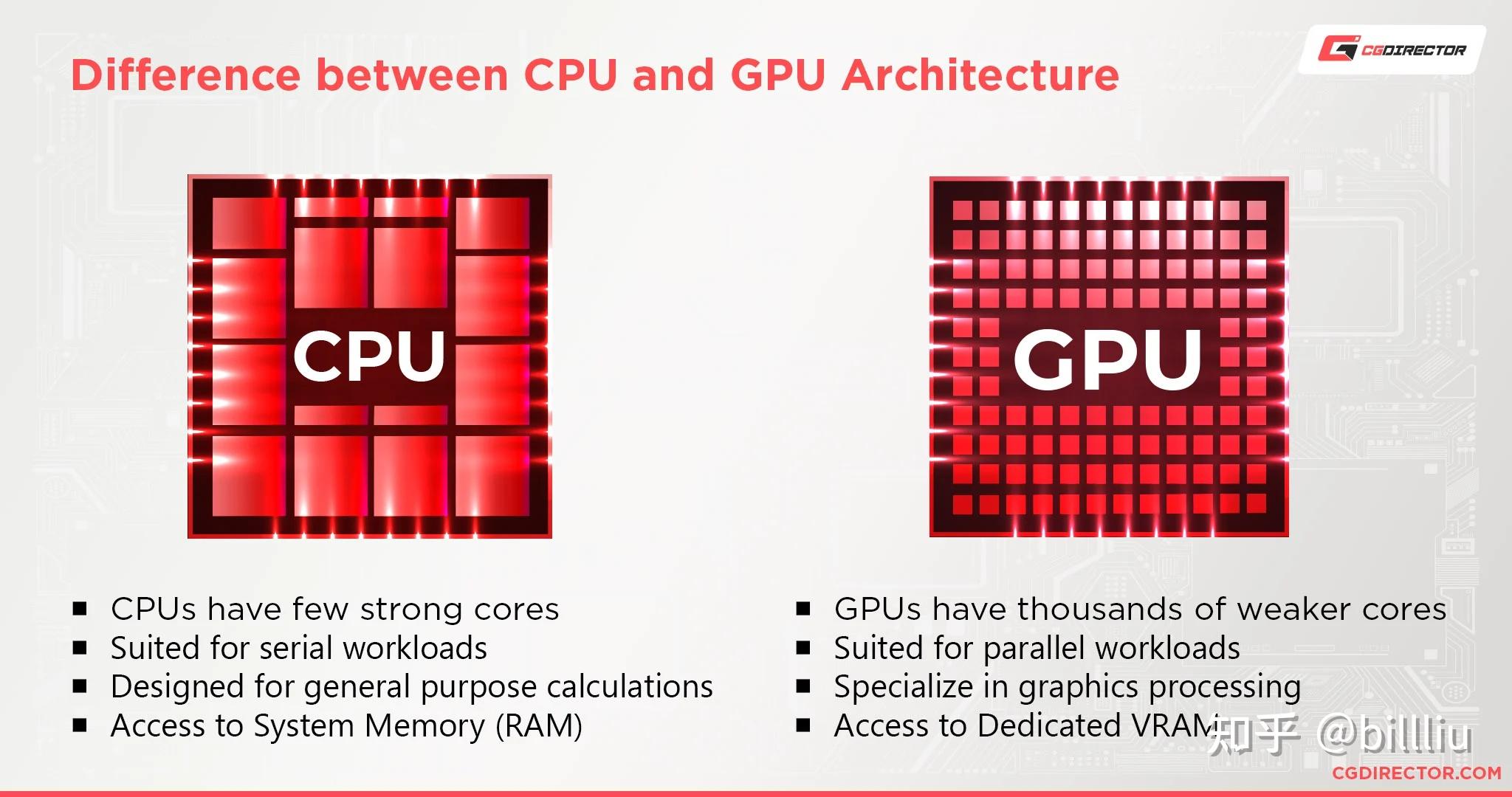

DDR,这便是双倍速率同步动态内存(DoubleDataRateSynchronousDynamicRandomAccessMemory),在现代计算机体系结构中占据着举足轻重的地位。其卓越的数据传输速度与低能耗特性使之声名远扬。初次接触DDR芯片电路原理图时,我为其精细巧妙的设计所折服。电路图中的每个晶体管、电容,如同交响乐中的每一个音符,共同谱写出了数据传输的美妙旋律。

深度探究DDR芯片运作机制,可知其利用上升沿与下降沿皆传送数据,从而实现数据传输速度提升至两倍之效。此独特工作模式为我带来挑战与乐趣并存,需具备深厚的时序及信号完整性知识。

电路设计的关键因素

在制定DDR芯片电路的设计方案中,需确定电源管理等几项首要考量。电压稳定性乃DDR芯片正常运行的基础,微小的波动都可引发数据丢失乃至系统崩溃。故而,需谨慎规划电源轨道与去耦电容,以保证电源的纯净与稳定。

接下来要点明的是信号完整性的重要性。鉴于DDR芯片需迅速处理庞大数据量,这就使得信号完整性显得尤为关键。为此,我在电路设计过程中,会对信号线的长度进行精确把握并采用适宜的终端电阻以避免信号反射。

时序分析的重要性

时序分析在DDR芯片电路设计中至关重要且极为复杂,需精准测算每一信号的传输延迟,以确保数据能在适宜的时刻传送至指定地点。为此,掌握并运用多种仿真工具对电路的时序特性进行模拟尤为关键,而在此过程中的反复调试与优化亦令我收获颇丰。

每次在仿真过程中攻克难题,我都体验到了犹如探险家寻获珍宝般的欣喜。这不仅仅源于技术层面的突破,更多是自我价值体现及对新领域探索的满足感。

电路布局的艺术

在DDR芯片设计中,电路布局可谓至关重要。优秀的布局能提升电路性能并降低电磁干扰。我致力于使信号路径短化,避免高速信号的交错,同时也精心布置电流供电与接地。

每当一副精细的电路蓝图完成,目睹其布局线路逐渐呈现于PCB之上,那份创造成果犹如艺术家作品圆满完成,既是满足也是对美的执着追求。

电磁兼容性挑战

针对DDR芯片电路设计,电磁兼容性问题极为关键。在高数据传输环境中,电磁干扰易对电子设备形成不良影响。故在设计过程中,我会着重关注电磁屏蔽与接地策略,以保证电路的稳定运行。

解决电子兼容性难题需超越常规思维,运用创新策略。在这过程中,既检验了专业素养,又激发出创造潜能。

电路调试的耐心与智慧

电路调试乃是DDR芯片电路设计中的核心环节及高耗时步骤。在此期间,我需运用各类测试手段以评估电路参数并寻找隐含的问题点。尽管调试过程充满变数,但正是这些未知因素使其充满挑战与乐趣。

每次我成功破解复杂调试过程中的难题,便会体验到侦探断案般的满足。这种满足并非仅来自于技术的精进,更是对自身耐心与智慧的认同。

持续学习的旅程

在当前瞬息万变的行业环境下,深知唯有不断涉猎新知识才足以紧跟时代发展步伐。DDR技术领域亦是如此,历代产品不断推陈出新,每个时期均有各自独特的性能优势与挑战等待我们去应对。为此,我始终保持对新技术的浓厚兴趣,积极了解并掌握最新科技动态,以期在设计过程中运用到最尖端的解决方案。

每当透彻领悟新技能时,均能感受到职业阶段性进展的欣喜之情,这种乐趣并非仅来源于知识积累,更为对自身职业发展及未来远景所做出的巨大努力投资的回馈。

结语与展望

回顾我从事DDR芯片电路设计之旅的过程,不禁感慨万分,充满骄傲与满足感。这段历程使我的专业技能得到显著提高,同时锤炼了我的耐心与才智。我坚信,随着科技日新月异的发展,DDR芯片在未来的电子领域必将发挥更为关键的作用。

在此,我想向诸位读者请教一个问题:您是否曾在自己的专业领域内,历经类似的探寻与成长之路?欢迎您在评论区分享您的经验,共同探讨与进步。若您对本文有所共鸣,恳请您不吝点赞与分享,您的鼓励将成为我不断前行的强大动力!