身处数字化领域的广阔空间,作为电子工程师,我潜心研究FPGA操控DDR3内存的复杂技术,这不仅仅是对技术深度的追求,更是心灵与技术的融合,精准高效的极致体验。

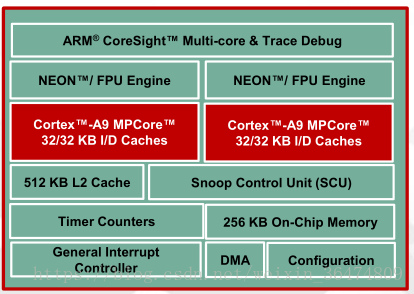

FPGA与DDR3内存的基本理解

FPGA(现场可编程门阵列)在我看来并非一个简单的芯片,而是宛如画板般的存在,让我得以在其上描绘复杂且精密的逻辑线路。而DDR3内存,作为高速数据存储领域的佼佼者,其每次读写都堪称速度与稳定性能的双重考验。当二者相互融合,如同搭建起了一座通往计算需求与实际实现之间的桥梁。

FPGA控制DDR3的核心原理

掌控DDR3内存机制,对我而言,不只是纯粹的技术实施,更是一种对至臻品质的执著追求。借助于FPGA的可编程特性,精准无误地生成DDR3所需时序信号,使得每次微调犹如工艺品的精细雕刻,努力在数据通信中达致最高效、最稳定的巅峰状态。

时序设计的重要性

在FPGA控制DDR3的过程中,时序设计起到了至关重要的作用,如同心脏的脉搏。每次时钟的滴答声预示着数据的流动。我为此付出了无数个日夜,以保证每个时序的精确无误。这不仅是对技术的追求,更是为了让每位用户在每次数据传输中都能体验到我们的匠心独运和专业精神。

错误处理与容错机制

研发过程中的探索必然伴随着差错。为防止DDR3内存错误影响系统运行,我们构建了精密的容错机制。此机制并非简单的代码堆积,而是如同编织一张严密的网络,确保数据在任何极端情况下的完整性和安全性。

性能优化与调试

在我看来,性能优化乃是无尽追求。在FPGA对DDR3的操控过程当中,探寻性能提升之可能性始终贯穿其中。而调试过程则类似于一场与难题的搏斗,每次成功解决问题皆使我更接近理想性能。

应用案例与实践体会

每项成功案例皆为技术精髓之体现,实证中,FPGA对DDR3内存的精准控制,既大大提升了数据处理效率,又增强了整体系统稳定性。这些宝贵经验使我深感理论与实践相结合的美妙之处。

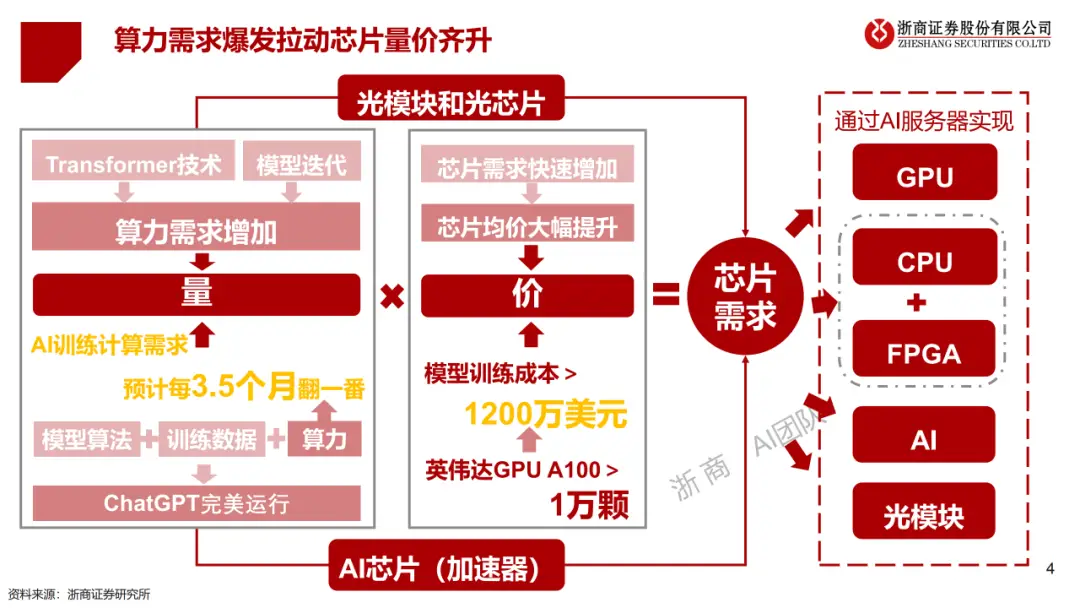

未来展望与个人期望

展望未来,我热切期望FPGA与DDR3内存技术的整合,期待借助此项应用让世界获得更大效益。作为技术工作者,推动科技和社会发展是我的使命,我愿为之贡献自己的力量。每一次技术革新都将引领我们走向未知的领域,激发无尽的想象力。