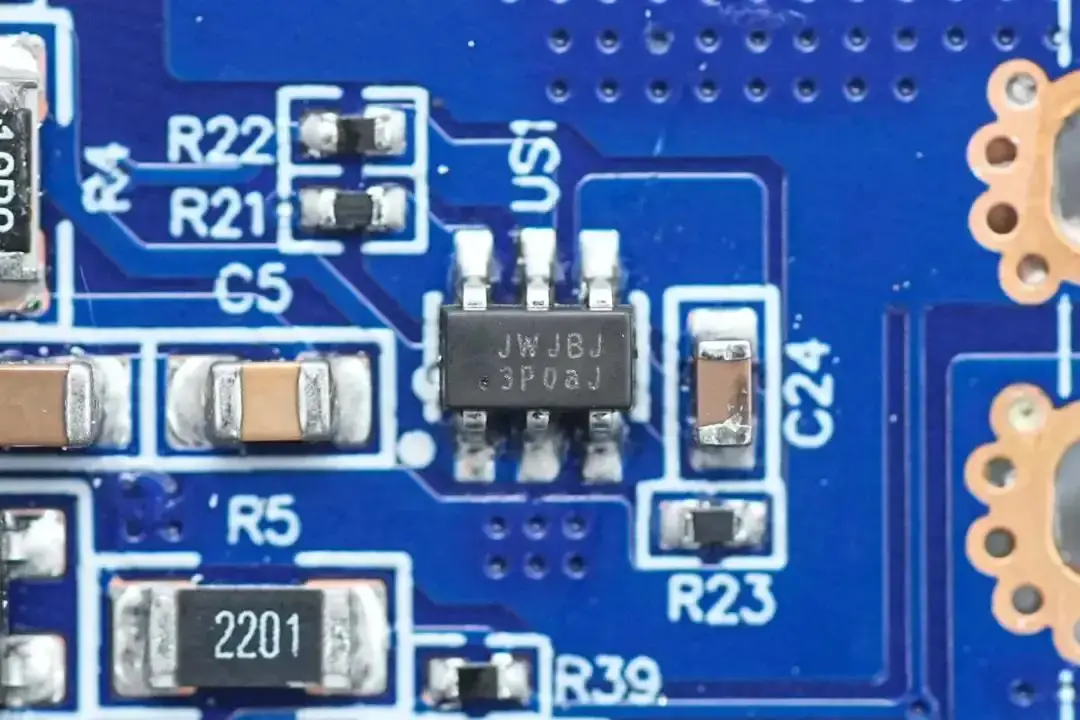

在成为半导体工程师的道路上,我对DDR(双倍数据传输速率)内存颗粒有深入研究,这类芯片内部具有精密电路且处理数据表现出极高效率。今日在此,愿将我在DDR芯片电路设计方面的经验总结出来,让您领略到这其中所包含的工程技艺及科学魅力。

DDR芯片的电源管理电路

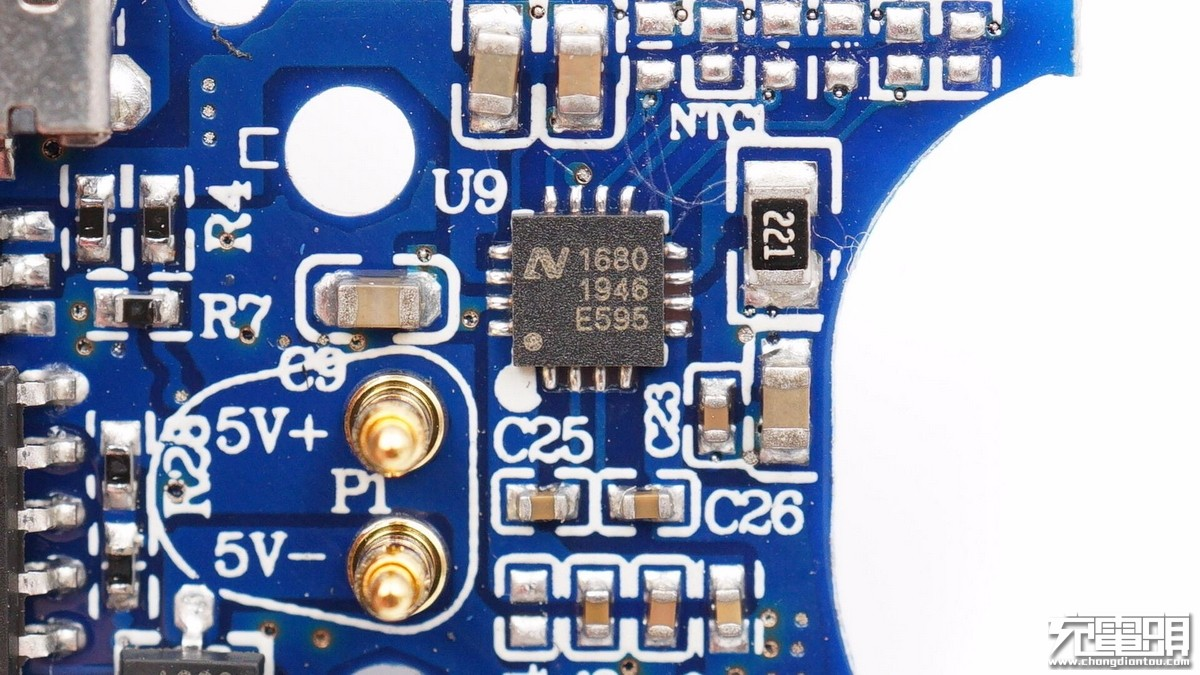

在DDR芯片组成中,电源管理电路具有举足轻重的地位。在此类电路设计初期,首要任务便是确保芯片得到稳定且高效的供电,这样既能保障性能,又会对能耗及可靠性产生深远影响。曾在某次优化行动中,为实现供电更为精细化的管理,历时数周调整各项电路参数,结果成功将芯片运行时的功耗降低了10%,从而提升了性能并为环境保护尽了绵薄之力。

电源管理电路的关键职责在于:降低能耗与稳定电压,特别是应对各种工作环境的挑战。对此,我们必须关注的是电路对负载变化的敏锐反应能力,以及其调节和控制输出电压水平的能力。精细化的电路设计在此显得尤为重要,因为电压的微小波动都可能波及整个系统的稳定性。

数据传输电路的设计挑战

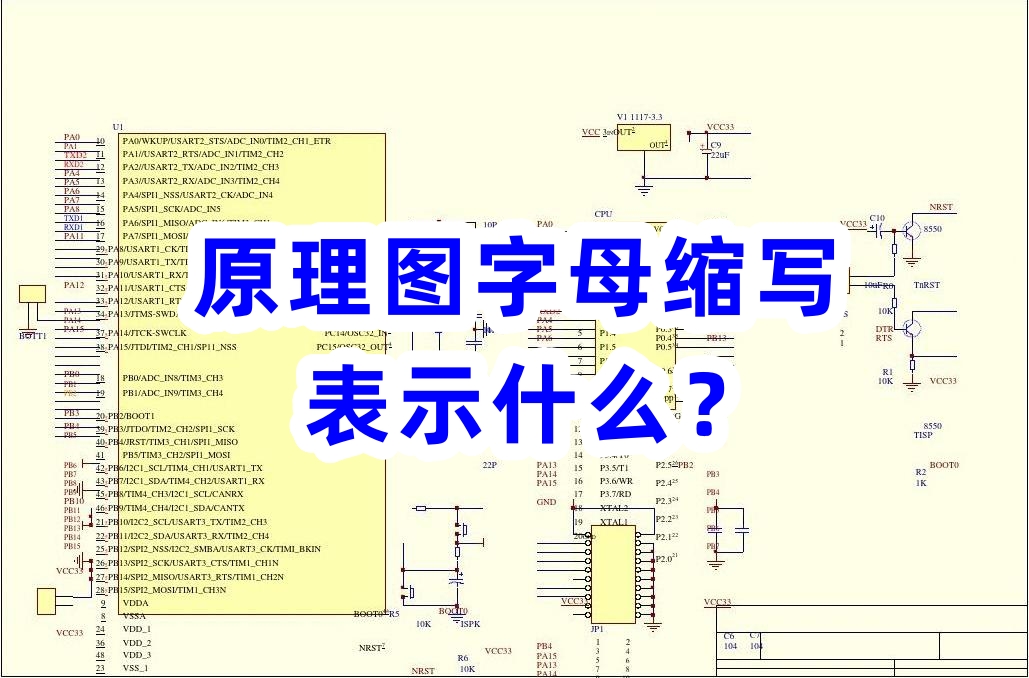

数据传输线路乃DDR芯片之核心组件,主要功能为实现内存与处理器间的高效率数据传输。在此部分,关键在于降低信号传输过程中的延迟及错误率。曾有一度,在调整数据通道时,笔者发现拓宽信号线宽可有效增强数据传输速率,但同时亦引出新问题,如更高耗能及更为繁琐的设计。

面临诸多挑战之际,我掌握了性能与成本之间的平衡之道。借助尖端的信号处理技术,我们得以在有限的成本下显著提升数据传输的稳定性及效率。这使我深刻理解到,设计绝非单纯的技术问题,而是一门艺术,需在种种约束中寻求最优解。

时钟电路的精密调控

在DDR芯片内,时钟电路起到了精密同步的关键作用。为保证其正常运作,设计者须保证时钟信号未出差错,尤其是频率及相位。有一回,我在设计新的时钟分布网路时遭遇了时钟偏斜难题。为了攻克此关,我深究电路布局与时钟信号传输特性。经过精心的布局优化和信号调整,终于成功降低了时钟偏斜,提升了系统的同步精确度。

此经历使我深入认识到,精准的工程操控,即便在微观层面,同样是达成高效运行的关键因素。任何细小改动均能引发全局性能的巨大改变。

错误检测与纠正电路的必要性

在DDR芯片的运行过程中,完整性电路扮演着确保数据无错传递的关键角色。当大批量数据传输遇到微小误差时,其带来的影响将不容忽视。为此,设计出一套高效、稳定的错误侦测机制显得尤为重要。在日常工作中,我需对各类错误侦测算法进行深入分析,以挑选出最符合芯片设计需求的方案。

此过程不仅需深厚理论知识,更需丰富实践经验。曾有一次,为提升新产品数据传输可靠性,我方引入新型错码纠错机制,实际应用效果显著优于预期。此次经历使我深知,创新并非仅限于技术突破,更在于对既有方法的深入理解与灵活运用。

功耗与热管理的电路设计

鉴于芯片性能提升带来的功耗增加及散热困境,在电路设计过程中需兼顾性能与能耗控制。此过程涉及到深度的电源管理与热量管理方案制定。笔者在设计低功耗模式电路时,就如何维持性能前提下降低功耗,遇到了极大挑战。通过采用动态电压频率调节技术,成功实现了在不损失性能的基础上,大幅度降低功耗的目标。

经历此过程后,更加明确了作为工程师,不仅要在技术方面有创新突破,同时也必须关注产品的可持续发展以及对环境的影响。每一个设计决策,均应以负责任的态度对待环境与未来。

接口电路的兼容性与扩展性

在DDR芯片的设计之中,接口电路的兼容性与扩展性至关重要。新技术的不断涌现使得接口规范逐步更新,这对电路设计提出了新的要求。为了满足兼容性的高要求,我面临着同时支持多种标准的难题。然而,通过模块化设计,我们成功地解决了这个问题,并为未来的技术升级预留了充足的空间。

此次设计经验让我深感灵活性与前瞻性的重要性,它们是电路设计中的关键元素。优秀的设计应既能满足当下需求,又具备适应未来发展的潜力。

测试与验证电路的重要性

至关重要的是,我们必须对电路进行全面的测试与验证。在DDR芯片研发流程中,这些工作有助于确认所有设计方案的准确性。在经历了一次复杂项目的测试阶段后,我深刻体会到测试电路设计的繁琐及必要性。借助精密的测试方法及其相关设备,我们有能力迅速发现并修正设计中的缺陷,从而保证芯片能达成预定的性能指标。

在这个过程中,我的技术与问题处理能力得到了提升,深感每个成功芯片的诞生,离不开严密的测试和验证。

总结与反思

从业多年来,我对DDR芯片电路有深刻理解。每次设计决策与电路优化皆是对技术极限的挑战,同时也助我实力不断提高。期待以个人经历启迪更多同仁热爱并投身于半导体行业。

本文落笔之际,不禁引发深思:未来半导体领域面临哪些重大挑战?敬请各位读者于评论区畅所欲言,共同探索这片充满无限可能的科技疆界。衷心期待您的认可,若本篇文章对您产生了积极影响,恳请惠予点赞与分享,使更多人从中获益。