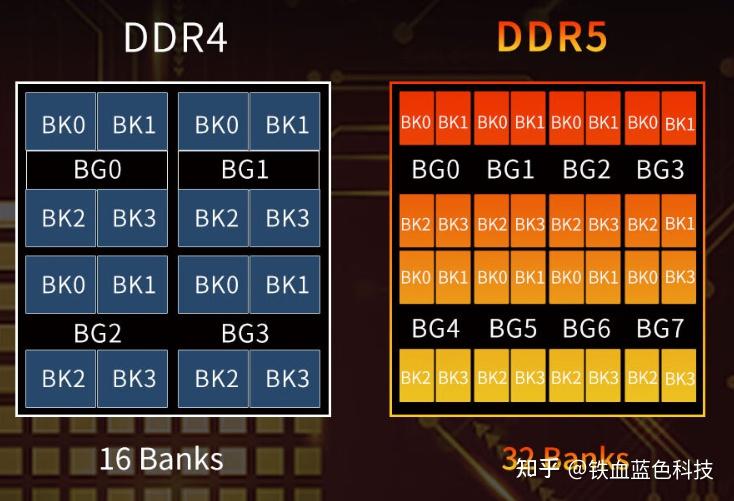

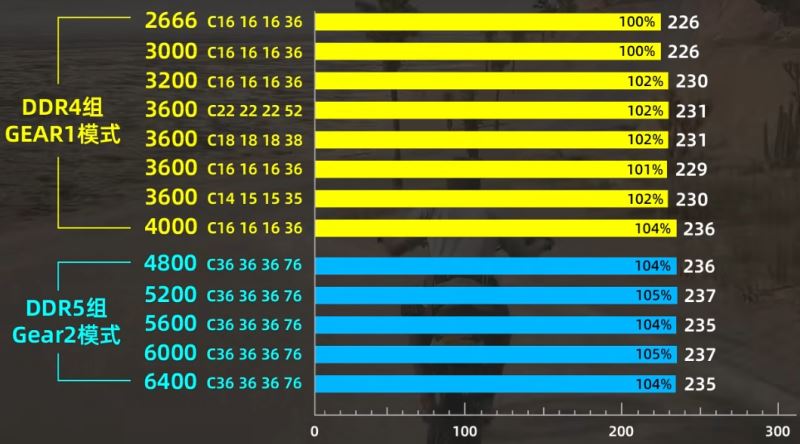

身为资深硬件工程师,我深知DDR5内存降频及时序控制之重要性。在设计DDR5内存过程中,严格的时序规定是维持其高效性能的关键因素。相较于DDR4,DDR5内存拥有更高的运行频率以及更为严苛的时序规范,从而确保了高速状态下数据传输的稳定性。而降频压时序则是在降低频率的同时,保障内存正常运作,防止数据传输出现误差。实践操作中,我们需依据DDR5内存的规格手册设定适宜的时序参数,以确保系统的稳定性与性能表现。

DDR5内存的时序特性涉及诸多方面,如读写顺序、预充电时机及活跃周期等。时序设定并非仅受内存自身性能制约,亦需考虑主板构造与电源稳定状况等元素。实际调试环节中,我们需反复测试与调整,以寻求最优时序组合,进而保障系统的稳定性与高效性。

DDR5降频对系统影响

在面对高温或电压不稳等特定环境时,DDR5内存的降频操作旨在确保系统的稳定性。由于高温或电压大幅波动可能引发数据传输错误乃至系统崩溃,因此适当调低内存频率可降低时序需求,从而提升系统稳定性。

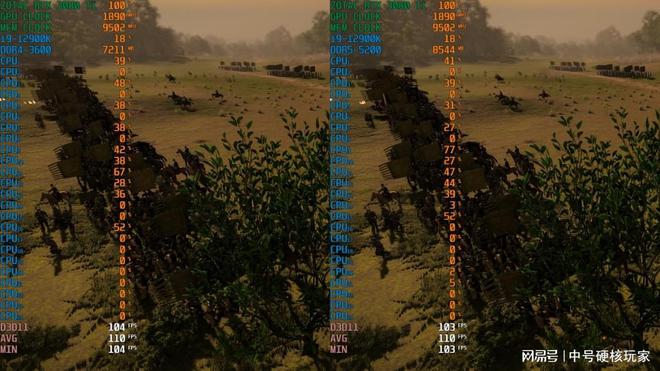

然而,DDR5内存降频将直接影响系统性能。当内存频率下降,数据传输亦随之放缓,进而影响整个系统的运行效能与响应时间。故而,实践运用过程中,必须面对稳定与效能的抉择,选取适宜的内存频率及时序设定,以满足系统需求。

DDR5降频压时序的调试方法

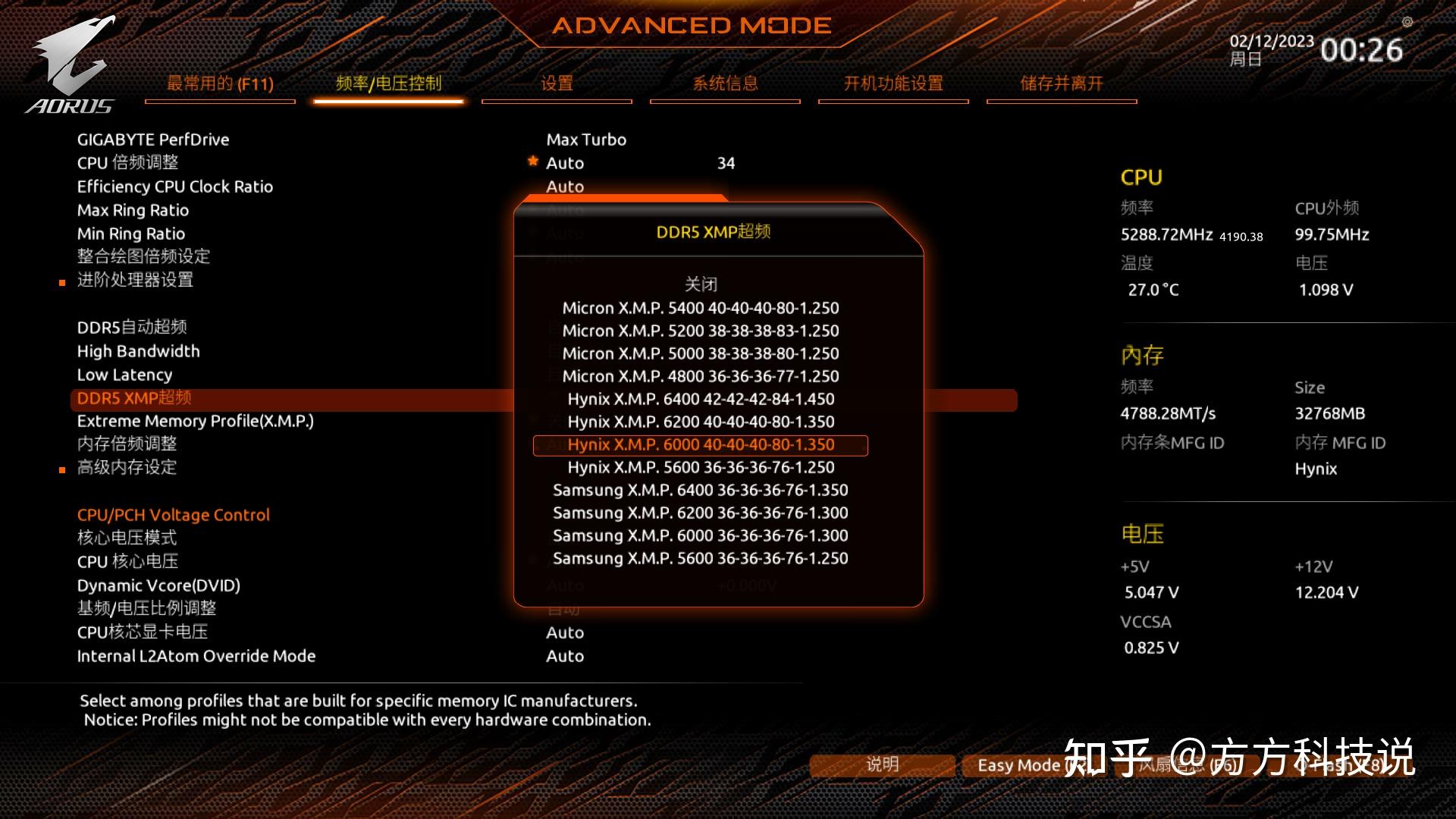

在针对DDR5内存调速与降低传输速度的过程中,为了验证并完善时序设定,我们通常运用以下几种常见手段。首先,借助内存制造商所提供的检测工具如MemTest86,对内存进行稳定性测试以确保时序设定的合理性。其次,通过调整时序参数,例如CAS延迟时间、预充电延迟等,观测系统稳定性及性能的变化,从而确定最优的时序设定。

此外,仔细查看系统错误提示及日志信息,如数据传输出错或内存访问超时等方面的迹象,都能帮助我们判断内存是否存在隐患。结合此类反映问题的细节了解,能及时针对内存时序设定不适当之处加以修正。在对DDR5内存进行降频压时序调试过程中,需保持耐心与细致,通过反复试验与调整,以寻得最适宜于系统运行的时序设定方案。

DDR5降频压时序的实际案例

近期,本人有幸参与一项关于DDR5内存降频压时序的调试项目,期间遇到一例颇有挑战性的问题。高温环境致使系统频繁发生数据传输错误及内存访问超时现象,严重影响系统稳定性。经深入剖析,我们推测问题可能源于内存时序设定不当。因此,我们着手调整内存时序参数,逐步降低内存频率与时序标准。

历经多轮周密的实验与调试,终寻得适于在极端气温环境中保持系统稳定的时序配置方案。此次调测经历使我深切认识到DDR5降频调时序之关键性,以及调试过程中所蕴含的挑战与趣味。唯有持续学习、实践,方能积累更丰富的调试技能及经验,从而提升系统稳定性与性能表现。

结语

探究DDR5降频压时序在硬件设计中的重要性与挑战,这无疑是一项专业化且精细化的工程,需要我们持续学习和实践来实现突破。只有在深刻理解了时序需求,并累积丰富的实操经验后,我们才能有效地优化系统性能,从而增强系统的稳定性。在未来的职业生涯中,我会坚持不懈地学习,以期进一步提升自身在DDR5降频压时序调试领域的专业素养,为硬件设计和开发事业贡献更多力量。