身为电子工程专家,每日与各式电子信号交融共处。今日,愿与诸君共享我对DDR信号高/低电平判定之感悟与体验,此不仅为技术之实践,实则蕴含科学探索之趣味。

DDR信号的基础知识

DDR(双数据速率)作为一项成熟的内存技术,其核心技术为每周期的上升及下降沿均能传输数据,较传统方案有双倍的性能提升。在这一过程中,正确识别高低电平尤为关键。电平高低是指信号电压的两种状态,高电平表示"1",低电平则表示"0"。

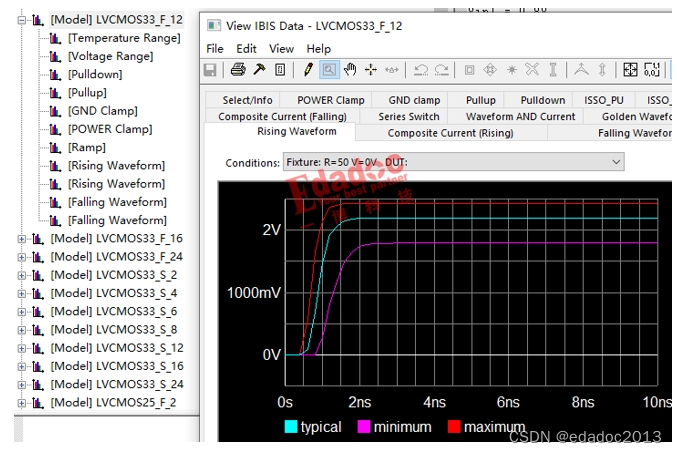

高低电平的物理特性

在物理层,DDR信号采用电压判别高低电平。正常情况下,高电平介于1.2V到1.5V之间,低电平则在0.2V至0.4V左右。要确保数据传输无误,必须对这些电压进行精准测量与调控。在此过程中,保持电平稳定及抑制噪声至关重要。

信号完整性的重要性

信号完整性为DDR信号处理之重要方面,涵盖了信号传输期间的保持与恢复。完美的信号可无误传递讯息,然而破损信号则易引发数据遗失或错误。故了解及维护信号完好对保障DDR系统高效运行至关重要。

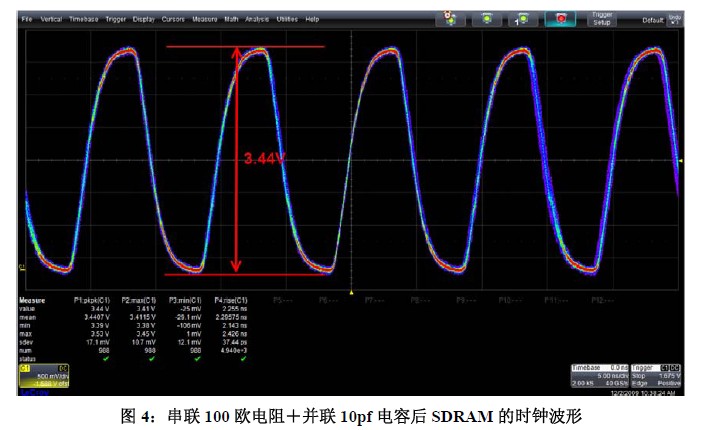

噪声对高低电平的影响

实践中,DDR信号易受各类噪声冲击,如电源波动、电磁干扰及信号间串扰等,此类因素均能对信号电平产生影响,从而阻碍数据准确识别。因此,实施高效的噪声抑制策略至关重要。

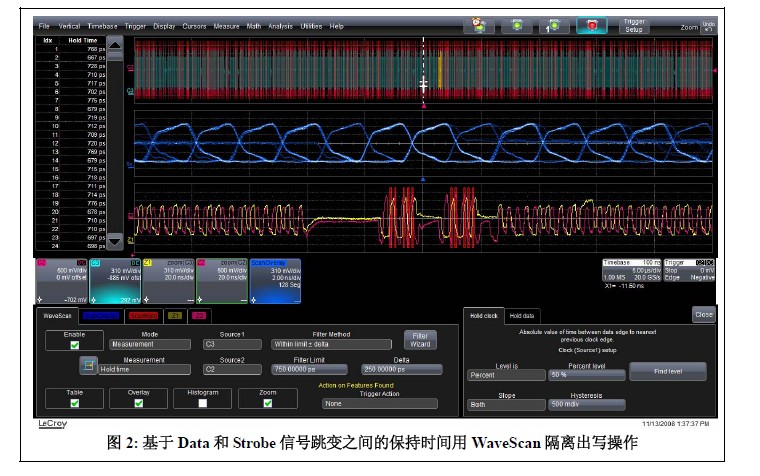

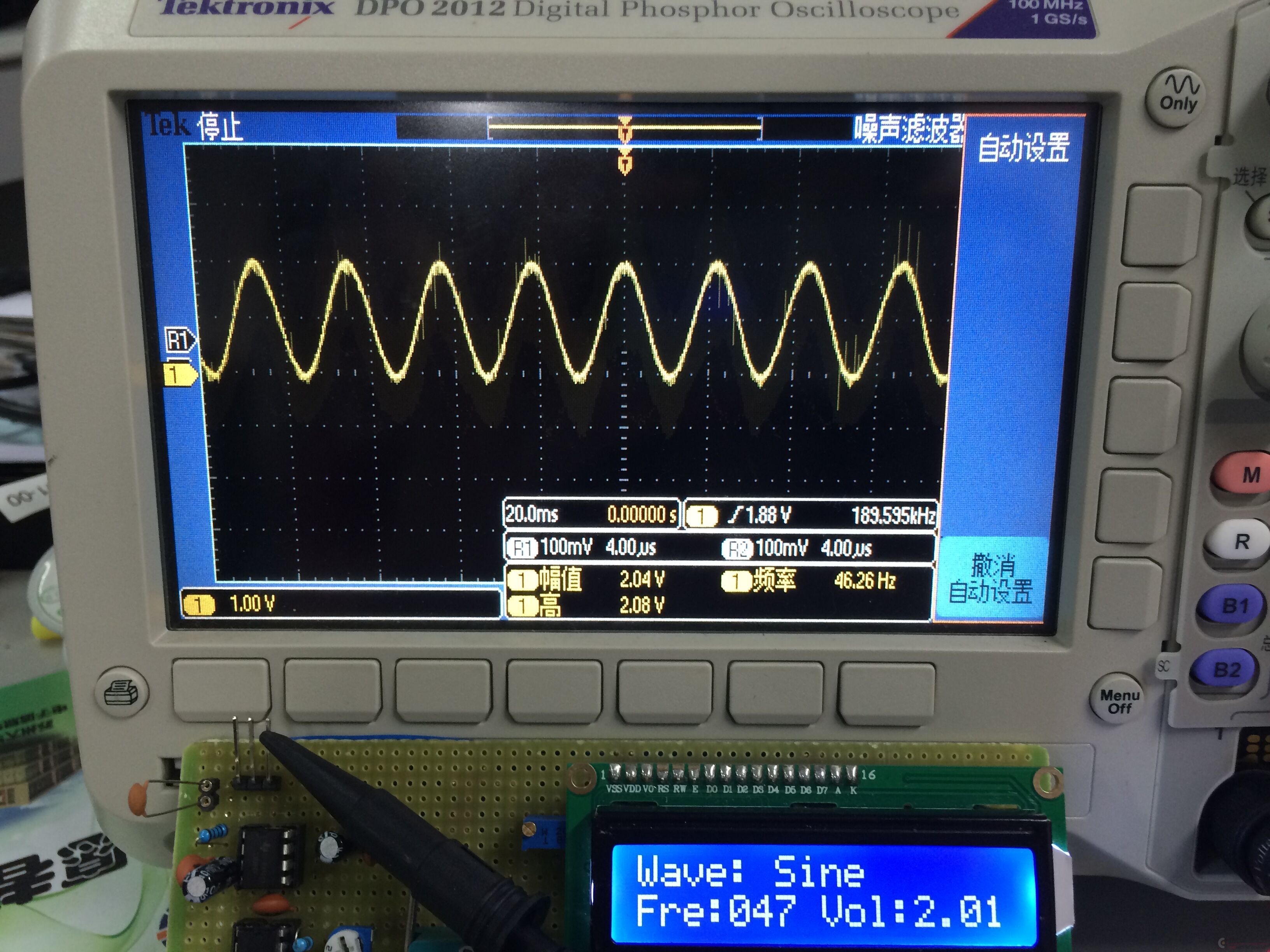

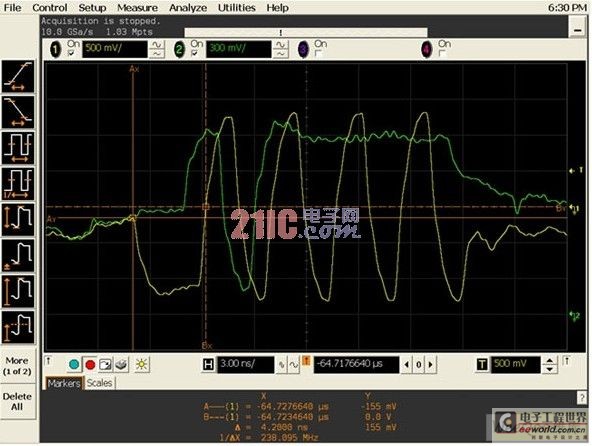

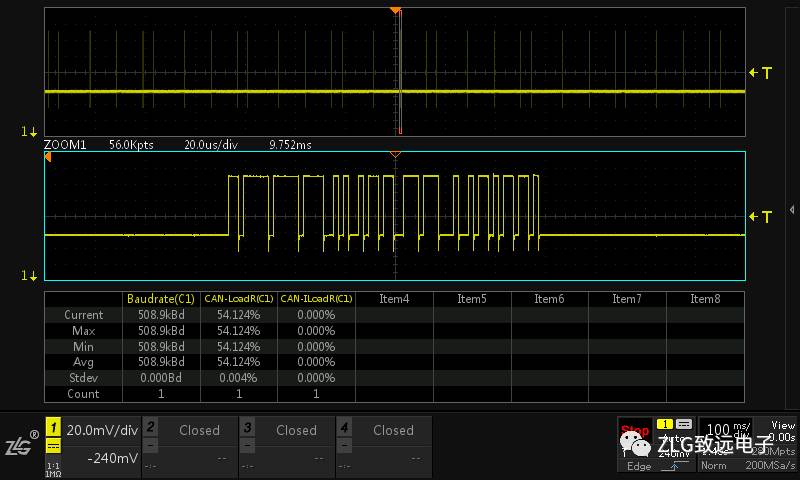

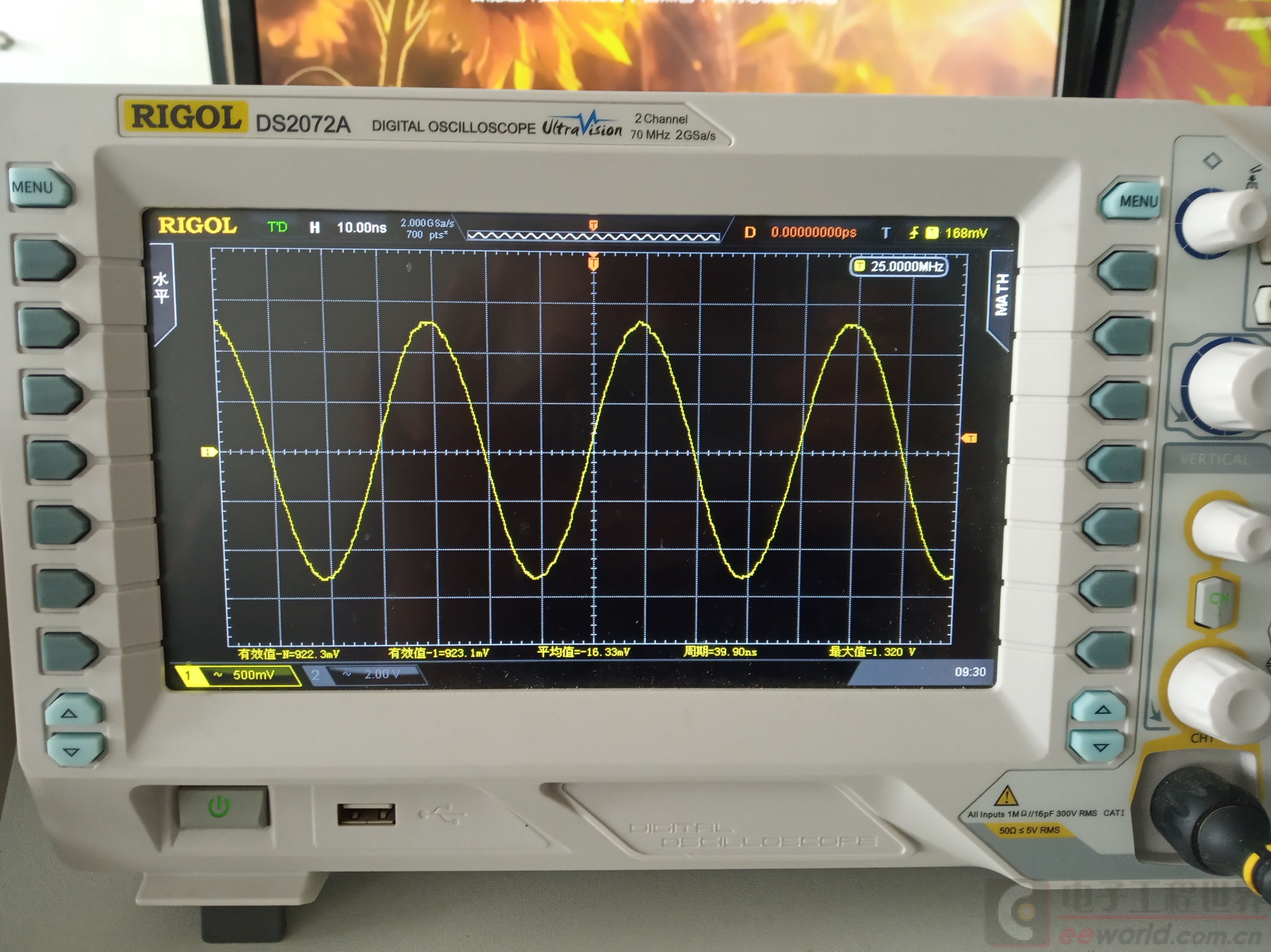

测试与调试技术

为保证DDR信号符合规范,必须实施精密的测试及调整工作。此过程中,往往需借助示波器,对信号波形进行观察,分析其电压值及时序特性。如此细致入微地检查,有助于在第一时间找出并解决信号传输上的任何异常情况。

实际案例分析

于职业经历中,曾遭遇多起关于DDR信号难题。如某系统运行时,内存读写速率骤降,排查后得知,乃电源芯片故障所致,引发电压波动,进而影响信号高低电平。经更换电源芯片及优化电路设计,终解此困局。

未来技术趋势

随着科技的日新月异,DDR信号处理技术亦在逐步完善,如新一代的DDR5,其在提升数据传输速度的同时,对信号的高低电平控制提出了更为严格的标准。因此,我们需要持续地学习并掌握新的技术,以确保我们始终站在技术前沿。

个人感悟

在数字化浪潮中,DDR信号高/低电平的判定不只是技工任务,更是现实与数字之间的关键纽带。每攻克一道技术难题,我便能体验到满满的成就感及满足感。这种感觉源于技术应用的成功,更源于其背后所展现的科学探索精神与创新能力。

结语与反思

此篇编辑报道旨在深入解析DDR信号高低电平判断的相关技术知识。在此过程中,读者可进一步了解科技领域中的科学精神和探索乐趣。同时,笔者也对各位读者在工作学习中所面临的技术难题表示关注。如果您愿意,请在评论文段分享您的经验,期待与您的深度交流。