身为电子工程师,我日常工作需深入研究各类电子元件及进行分析,今日将为各位分享关于DDR3内存之信号学知识。DDR3,亦称第三代双倍速率同步动态随机存取存储器,乃现代电脑系统中必不可少之组件,因其信号系统之复杂与精密性,对电脑整体稳定性具有重大影响。

DDR3内存的基本信号概述

DDR3内存主要由四种信号构成:控制信号、地址信号、数据信号及时钟信号。其中,控制信号涵盖了片选与读写指令等,用以操控内存运作;地址信号用于传递内存地址信息;而数据信号则承载具体的数据内容。时钟信号作为整个运行过程的定时参考,保证各操作均按预定时间进行。

控制信号的详细分析

DDR3内存运行的指令核心即为控制信号。如片选信号启用指定内存模块,读写命令人机交互指令数据读取及写入方向。虽非直接涉及其数据传输,但确保内存操作的精确与高效。我之实践经验认为,严格把控此类信号以提升系统性能乃至关重要。

地址信号的重要性

DDR3内存中的地址信号发挥着定位数据的重要作用。所有数据皆被精准地存放在内存相应的单元内,而地址信号则是引导系统找到这些地址的关键。设计过程中,我深感地址信号布线对精确度的影响不容小觑,不当布设甚至可能引发信号干扰,进而威胁到数据读取与写入的准确性。

数据信号的传输特性

在DDR3存储器内,数据信号是其主要沟通形式。在时钟脉冲的指挥下,这批信号以极高速度在存储器与处理器间往返传递。由于速度迅猛,对于信号的完整性要求极为严格。对此,我们需借助高速示波器进行数据信号质量的监测,以保证无任何失真现象发生。

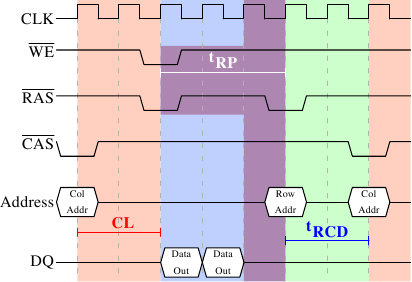

时钟信号的同步机制

时钟信号是DDR3内存的生命线,为其运作提供了明确的时间刻度。其中的同步机制,堪称时钟信号的灵魂,确保了内存操作的精确同步。在无数次的项目实践过程中,我们深知时钟信号的设计是对工程师技术的最高挑战,注重每个微小细节的设计才能有效防止时序异常。

信号完整性在DDR3内存中的应用

信号完整性作为检测DDR3内存性能的关键因素,涵盖了信号失真、噪声以及串扰等多重影响因素。实际应用过程中,为了保障系统的稳定性,我需谨慎进行精密电路设计并严密进行信号测试,这皆为保证信号完整性的关键要素。

DDR3内存信号的测试与优化

为确保DDR3内存具备最优性能,必须进行信号测试与优化。本人凭借专业测试工具,以确保对信号质量进行准确监测,并依据测试结果精准地调整电路配置。尽管此过程略显复杂,然而每次优化均可大幅提升系统性能。

未来DDR3内存信号的发展趋势

随着科技飞速发展,DDR3内存的信号处理技艺日益精进,如传输速度显著提升与能耗大幅降低。身为电子工程师,我对此类创新技术寄予厚望,深信其必将引领电子领域的全面进步。

本文旨在深化读者对DDR3内存信号系统的认识。每个信号宛如跃动的音符,共同谱写计算机系统和谐之章。最后,我们在此向各位读者提问:在实际生产与生活中,您又是怎样运用DDR3内存信号知识的呢?请不吝赐教于评论区,同时恳请为本文点赞及分享,让更多人探索DDR3内存的神秘世界。