身为电脑硬件领域的资深爱好者及技术博主,本人对于全新世代的DDR5内存技术怀揣无尽好奇心与热忱。此文中,将为您揭示个人在设定DDR5内存时序过程中的经历与心得体会,期望对志同道合者有所裨益。

初识DDR5内存

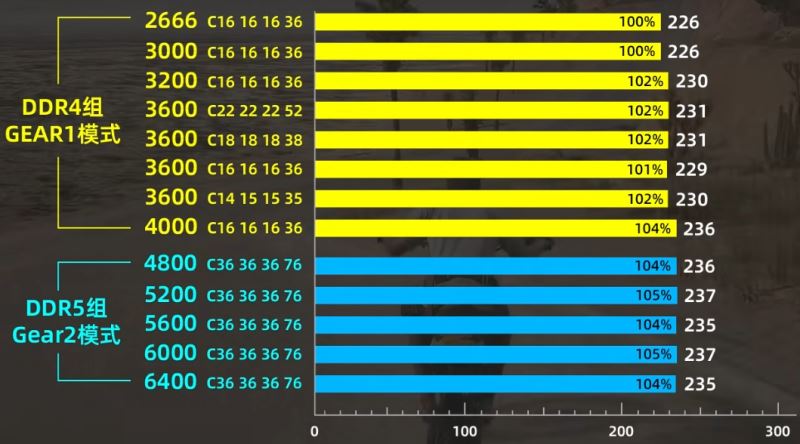

初次了解DDR5内存后,其较高的运行频率及巨大的数据带宽吸引了我。然而,如何精确调整时序也成为了新的难题,DDR5内存相对上一代在时序设定方面显得更加繁琐,这项困难无疑为升级之路带来了更多困扰。

深度研究DDR5内存技术规范后,领悟到时序设置的精确度是实现内存性能最大化及保证系统稳定性的关键所在。每一个细小时序调整皆能对系统性能带来显著影响,成为一项既充满挑战又充满探索乐趣的任务。

时序设置的基础知识

在更深入探讨之前,我们先对内存时序进行简要概述。内存时序主要涉及四个重要参数——CL(CAS延迟)、tRCD(行地址到列地址延迟)、tRP(预充电延迟)以及tRAS(行活动周期)。这几个参数共同影响着内存模块读取和写入数据的速度与效率。

历经无数次研读技术文献与参与论坛探讨,我决定亲自调整相关参数,并详细记载每一步操作所引发的系统反馈,包括性能提升或不稳定表现等细节。尽管过程繁琐耗时,却显著加深了我对内存运作机制的理解深度。

实战调整:我的第一次尝试

首次涉足DDR5内存时序调整工作,我曾满心激动却又充满警惕。细致入微地调整BIOS中的CL值后重新启动电脑,庆幸的是我成功开启了系统,并发现系统速度有了微微的提升。

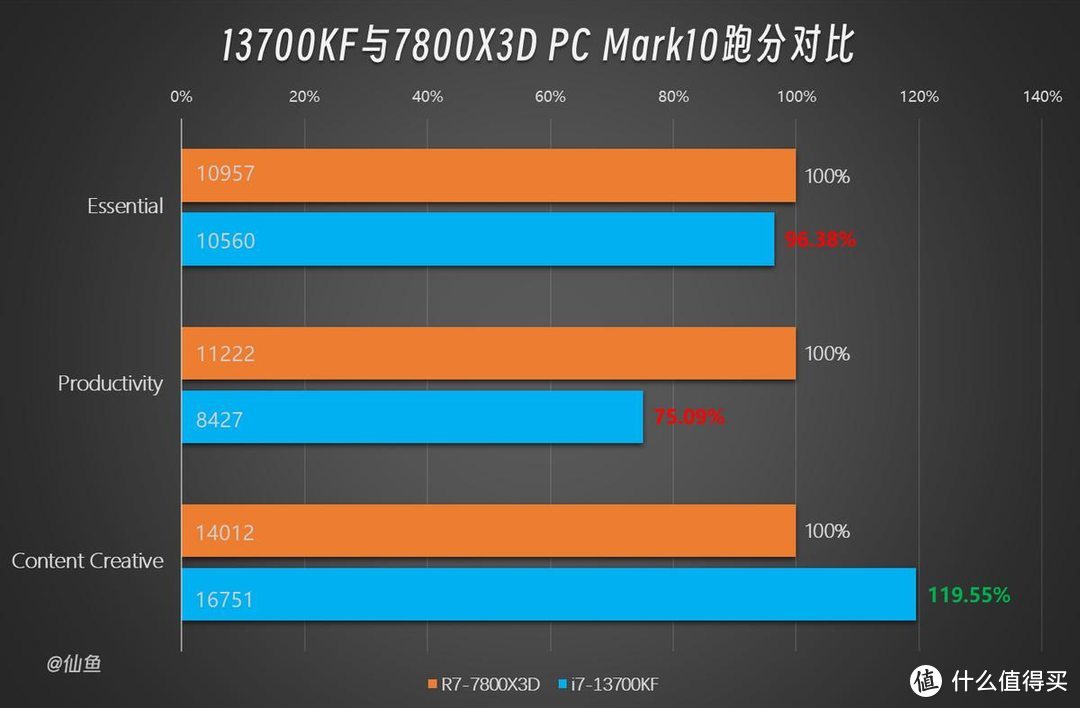

此次成功的尝试给予了我高度的自信心与动力。我持续地调整各项时序参数,每个循环都要经过严谨的测试环节,包括运行各类高压压测程序以及基准测试等。通过无数次尝试与探索,最终确定了最适宜我的系统的时序设定。

遇到挑战:不稳定的问题

然而,我在研究过程中也并非一路平坦。曾有一次,在努力实现更快速度而尝试降低时序之时,系统频繁出现蓝屏甚至崩溃现象。至此,我方认识到过度降低时序可能导致系统不稳。

为解决此难题,深入探究技术资料及他人经验后,经过精细调整电压值以及回归保守时序设定,终于使系统重归稳定。此番经历让我深刻领悟到:性能固然重要,但系统稳定性始终应置于首位。

分享我的经验

历经数载尝试与微调,我终于决定将我所掌握的知识和取得的成就,公之于众。期待能借此机会,助正探寻DDR5内存时序设定之道的同仁们一臂之力。

记录每一步骤,囊括成功与失误,共享历程以期共进共善,解决技术探研所遇难题。

展望未来:DDR5内存的发展

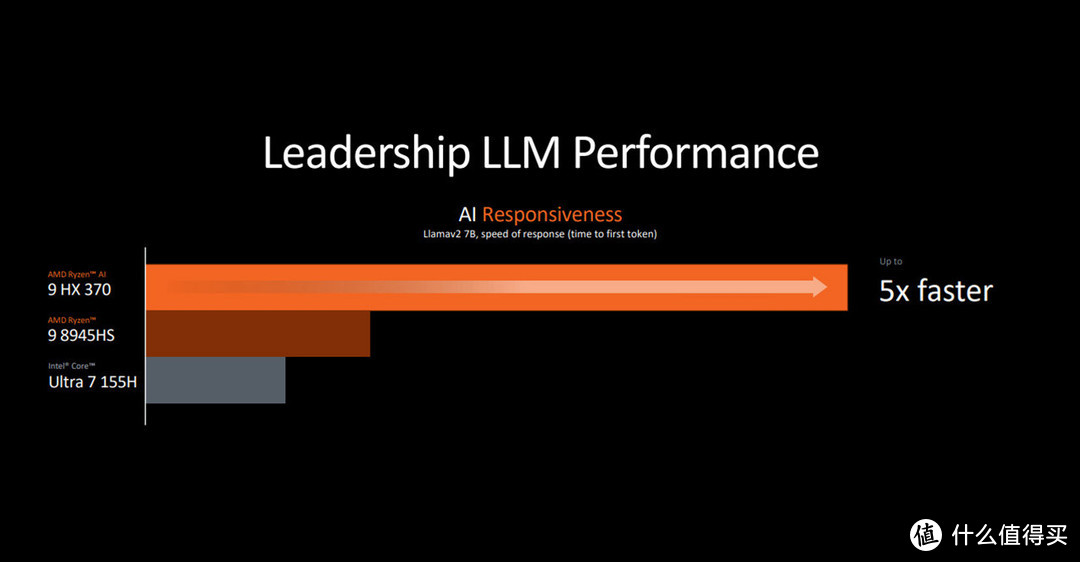

展望未来,本人对DDR5内存的前景充满热忱。伴随着科技创新的持续深化,必将带来更卓越的性能与稳定性。同样,我期望吸引更多业内精英与专家的参与,携手推进内存技术的繁荣。

在本文结语之际,我们希望抛出一个问题给广大读者:在您所从事的探索及实践过程中,对于内存性能与稳定度之间的权衡策略是怎样的呢?欢迎在留言区分享宝贵经验与见解;同时也期待得到您的赞赏与分享,让更多同仁从此次探讨中获益。