身为深入研究嵌入式硬件设计之士,对于全志H3处理器的DDR(双数据率)布线设计颇有心得。此设计环节对系统整体性能与稳定至关重要。本文将分享我在全志H3DDR布线设计过程中所遭遇的挑战及应对策略。

全志H3处理器概述

全志H3乃四核Cortex-A7处理芯片,嵌入式与多媒体领域皆有应用。凭借卓越性能与节能优势,获得市场热烈追捧。其中,DDR接口线路铺设至关重要,影响着内存读写速率及数据稳定传输。

DDR布线的重要性

在电路设计中,DDR布线不仅是技艺,更是艺术的体现。良好的布线可保障数据传输之高速与稳定性,反之则可能引发系统故障或性能衰退。我深知每一个细小布线选择皆可能对整个系统的效能产生深远影响。

布线前的准备工作

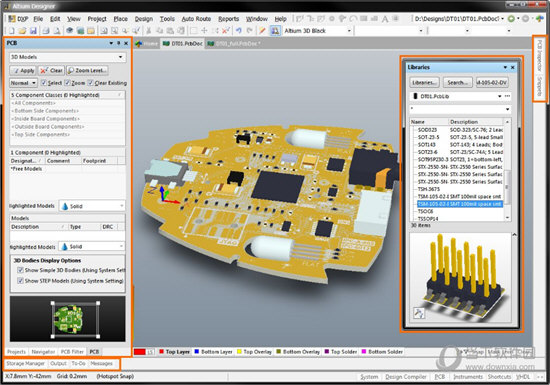

在工程布线前,我会进行深入细致的准备工作。首先,我研读全志H3的数据手册,以掌握DDR接口的电气特性以及布线规范。其次,我会借鉴过往项目经验,对潜在问题进行解析,并设计对应对策。

布线中的挑战与对策

实操环节中,面临诸多技术难题。如,如何在狭小空间内保证最佳信号质量;如何合理控制布线距离以降低时序误差等。为此,我不懈尝试与改进,逐步探索出实用高效的解决策略。

信号完整性的保证

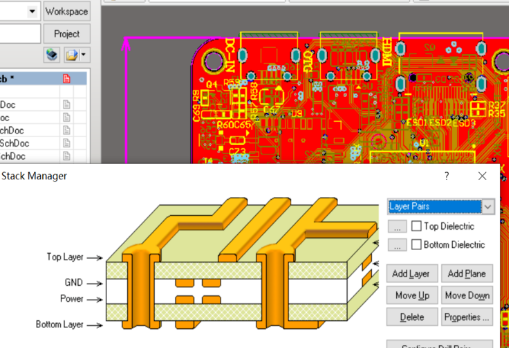

DDR布线中的信号完整性是关键考量因素。为确保这一点,实施了严谨且精细的线长管理、采用差分对技术进行布线以及科学安排地平与电源平面分布等策略。以上举措大幅提升了信号品质及系统稳定性。

时序问题与优化

时序问题在DDR布线中尤为重要。经过细致地研究时钟与数据线的布局,我有把握地确认它们能满足高标准的时序要求。通过精准控制线路长度及合理布置时钟,我有效降低了时序误差,从而提升了系统的运行效率。

成本与性能的平衡

在电路设计过程中,成本和性能间需寻求最佳平衡点。我理解,提高性能通常意味着增加成本。为此,我努力在设计阶段探寻性价比最优之策。通过精进布线策略及精选适宜材质,我得以实现性能满足需求且总成本可控的目标。

测试与验证

在完成实施布线设计后,将进行严谨的测验与核实。这环节包括采用精密的测试仪器对方案进行信号连贯性测试,及运用软件模拟技术,对系统整体性能进行检验。不论是何种类型的测试,它们都可视为是对设计方案的一次检讨,也是对个人工作成果的肯定。

总结与反思

在本次全志H3DDR布线项目中,深度体验到电路设计之艰难与魅力,无论是对每个环节的精细掌握还是每次决策的深思熟虑,令我加深了对硬件设计的理解及认知。我坚信,唯有持续学习与实践方能提升设计实力

在全志H3DDR布线设计过程中,我直面各类挑战与困扰,同时亦积累了丰富的经验并获得了满满的成就感。在此,我希望广大读者以分享自己在电路设计中所面临的挑战经历为契机,进行深入交流与学习,共同推进电路设计领域的进步。若您认为本文对您有所裨益,敬请不吝点赞与分享,让更多人从中获益。