自涉足电子工程研究领域以来,DDR4内存技术已成为我关注的焦点。关于时钟端接,我有着深刻的理解与实践经验。今日,愿与各位共享此段探究历程,期望对诸位有所启迪。

一、时钟信号的重要性

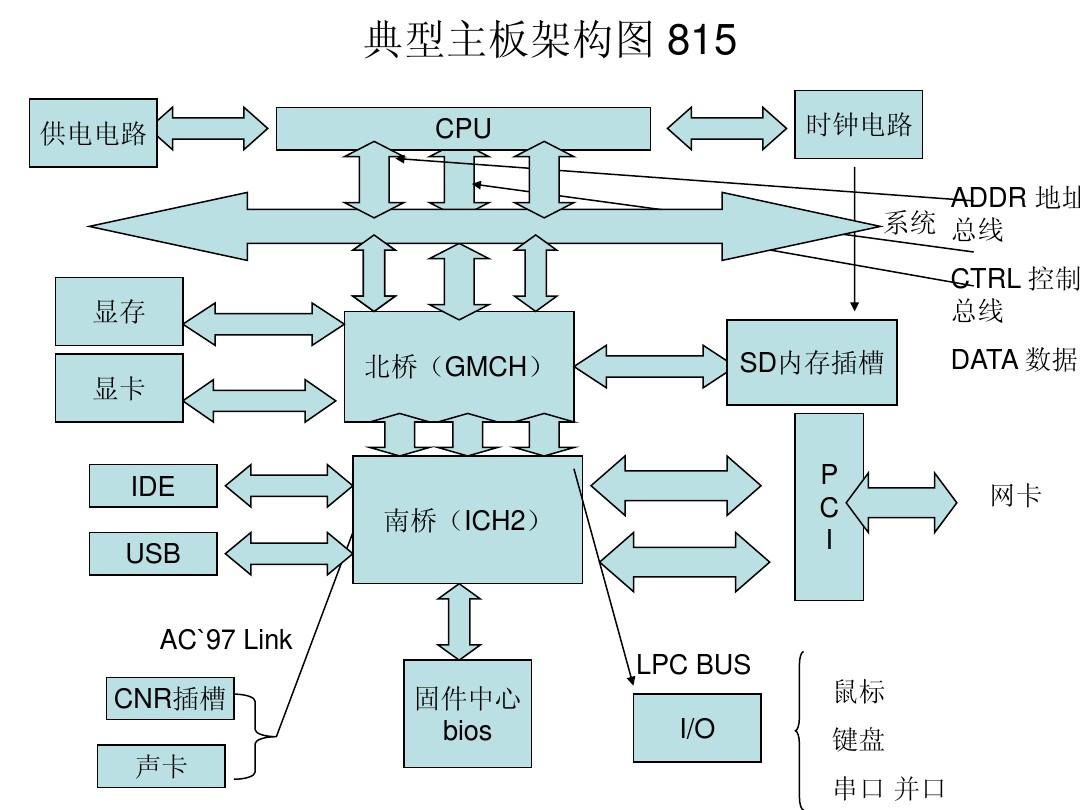

在DDR4内存系统中,时钟信号担当关键职责。如同音乐指挥,保证数据精准有序传输。我深知时钟信号稳定性与准确度对整体性能起到决定性作用。我曾负责的项目因时钟信号问题导致数据丢失,使我深切理解优化时钟连接刻不容缓。

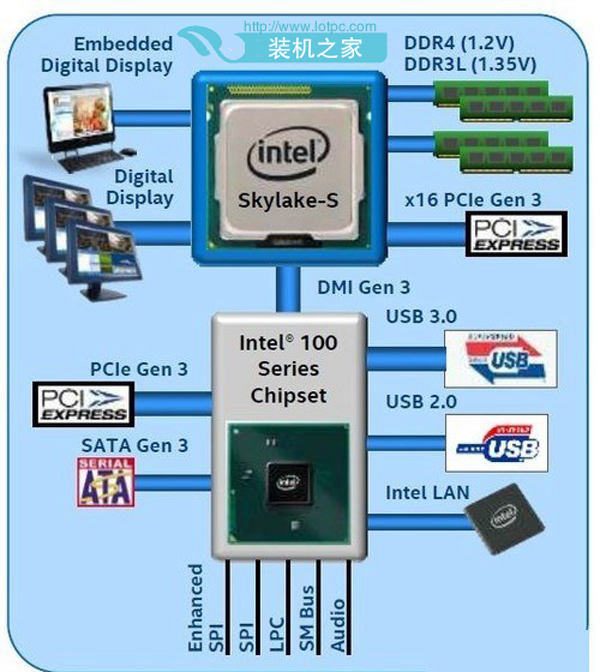

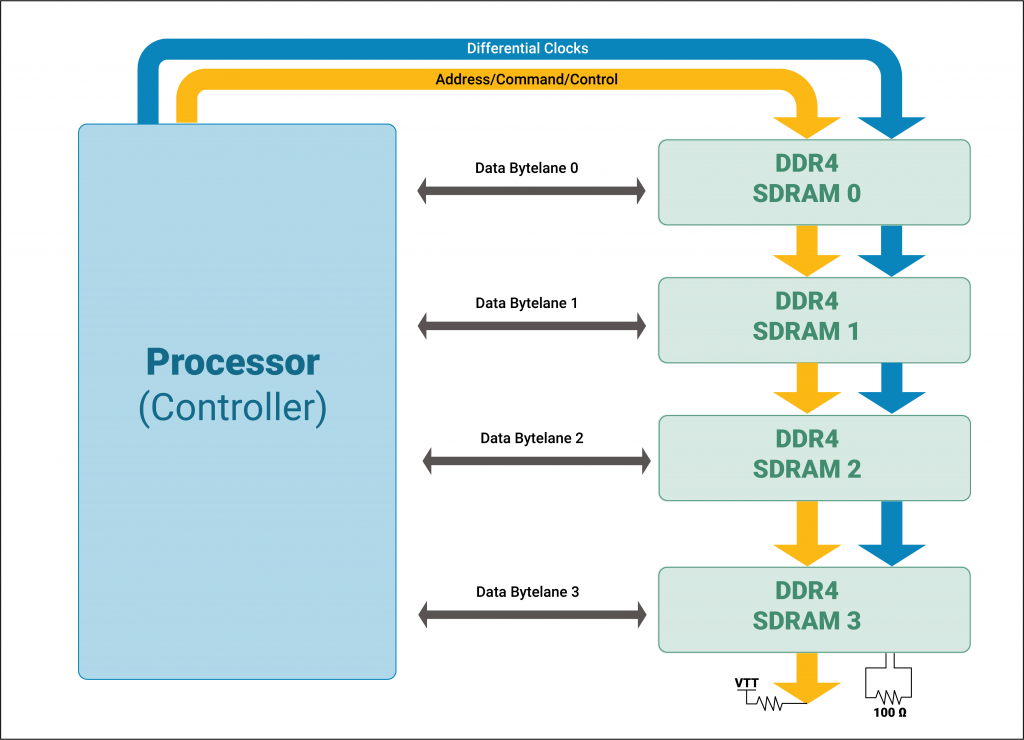

二、时钟端接的基本原理

为确保时钟线信号完整,需采取时钟端接技术降低其反射与串扰。DDR4内存模块中的时钟端接常采用串联端接或并联端接。理论知识的领悟或许稍显枯燥,但当成功构建一套稳定的时钟端接电路时所带来的成就感无以言表。

三、实际操作中的挑战

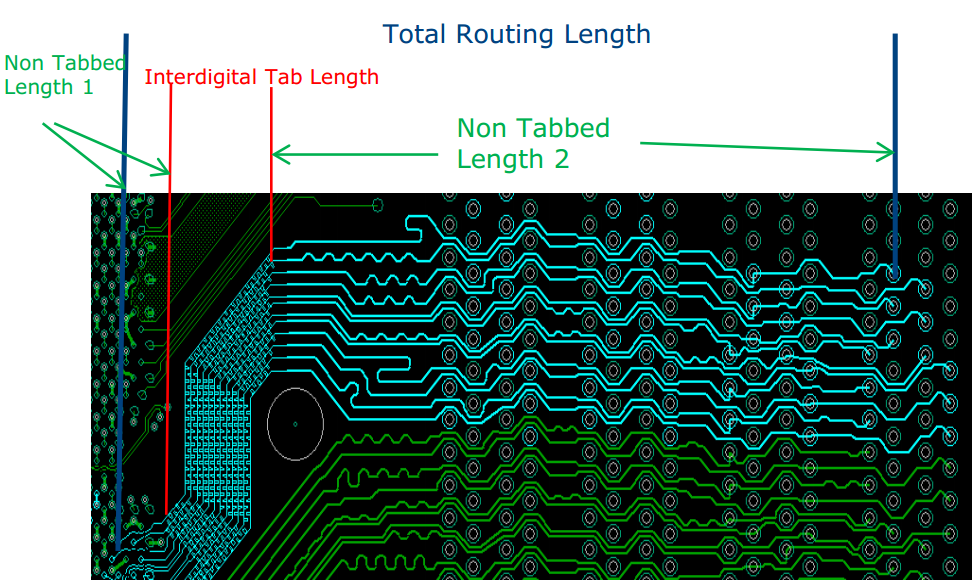

实践中所面临的时钟终端设计与调试实属具有挑战性。诸多因素需兼顾,如电路板材料、布线线长宽及周边电路干涉等。每一次参数微调皆须长时间反复验证,以确保时钟信号波形符合预期。该过程虽繁琐费时而乐享其探究之乐趣。

四、时钟端接的优化策略

为提升时钟信号质素,我们采用了诸多优化策略。如预先对设计进行信号完整性分析,预判潜在故障;在电路版布线时,确保时钟线与其它信号线远离以减轻干扰影响等措施。同时,选用优质的端接电阻及电容也是实践经验的总结结晶。

五、时钟端接与系统性能的关系

完善的时钟端接对整体系统性能具有重要影响力。经过实验考证,优质的时钟端接有助于提升数据传输速度及稳定性,特别是对高速运行的计算机系统而言尤为关键。我深感,若每位电子工程师皆能重视并深入研究时钟端接环节,必定能推动电子产品性能实现大幅进步。

六、时钟端接的未来趋势

随着科技持续进展,DDR4内存标准亦不断升级。时钟端接技术必将随之日新月异。预期不久将来,智能化、自动化时钟端接方案将成为现实。身为电子工程师,对此翘首以待,并决心尽己所能实现之。

七、我的心得与感悟

回顾对DDR4时钟端接的深入研究历程,收获颇丰,包括耐性与细致的培养以及对技术探索的热爱。成功解决每个难题,使我深信细节决定成败。希望我的经验分享能对同行们有所助益。

文章结尾:

此文是否加深了您对DDR4时钟端接的理解?您在实际工作中是否遇到过相似问题?欢迎在评论区分享经验与见解,我们共同探讨。若您认为本文对您有所助益,敬请点赞并分享,您的支持将成为我努力前行的动力。