电子工程领域中的硬件设计,每一次皆为挑战与乐趣并存的奇妙之旅。身为电子工程师,我曾有幸参与多项DDR3内存模块设计项目,实践过程加深了我对此领域的认知。本文将分享我在此过程中的心得体会,以及在DDR3硬件设计规范实施过程中面临的各项挑战及其应对策略。

DDR3内存技术的基础

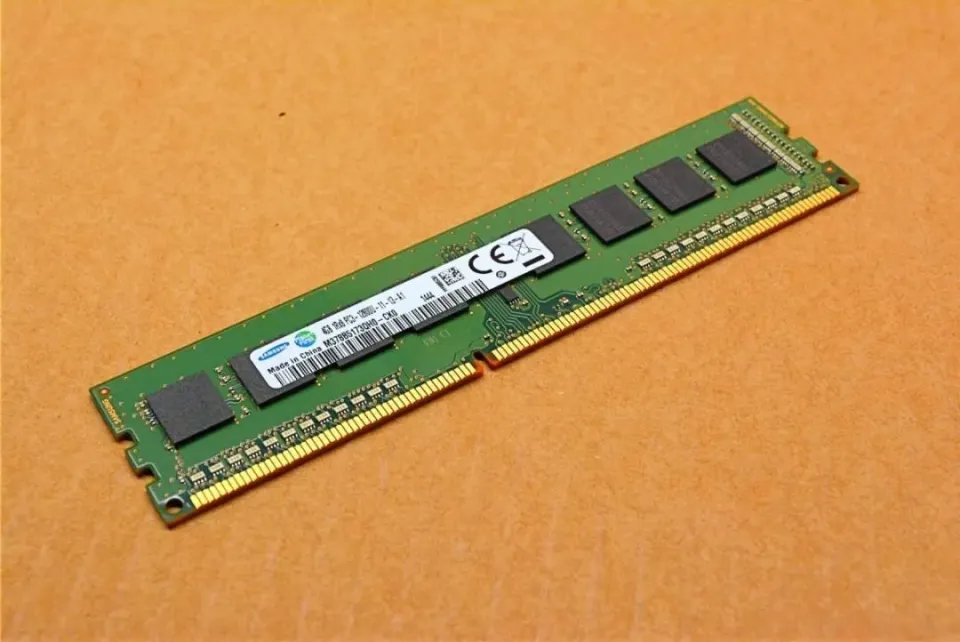

DDR3,即第三代双倍速同步动态随机存储器,在计算机存储技术革新中发挥着关键作用。相较于上一代产品DDR2,DDR3以其更快的数据传输速度及更佳能效表现脱颖而出。在实际设计过程中,深入了解并掌握DDR3的这些核心特点显得尤为重要。为了实现高效能与节能环保的双重目标,我需确保设计方案在保证性能的基础上,充分考虑到能源消耗问题。这既是对技术深度理解的检验,亦是对设计精细度的挑战。

在设计DDR3模块过程中,首要考虑的因素便是电气特性。与DDR2所采用的1.8V相比,DDR3所需的电压仅为1.5V,这便需我们重新调整电源系统以适应此差异。尽管电压降低有助于节能,却也使设计更为复杂,原因在于较低的电压会导致信号裕度减小,从而提高了对信号完整性的要求。

信号完整性和时序的关键性

在DDR3设计领域,信号完整性问题堪称主要挑战之一。伴随着数据传输速率的日益提高,信号速度亦相应攀升,这便要求我们精准调控信号的传输延迟。所有数据线与时钟线均需严格遵循设计准则,以保证信号能于恰当时刻抵达正确位置。

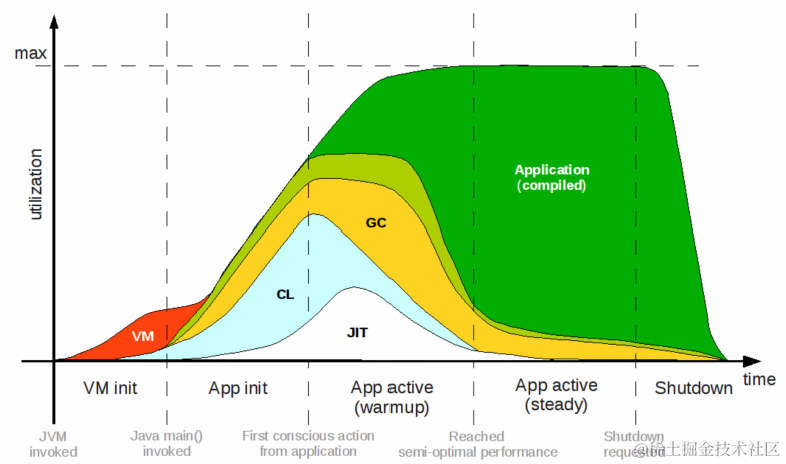

在探讨时序问题时,我会借助于仿真软件以预计及验证设计成果。模拟运算有助于洞察潜在的时序矛盾,并即时调整设计策略。这一实践使我更加认识到预测性与预防性设计之举的至关重要。每次仿真揭示的信息犹如探寻未知世界的引路标,指导我逐步改良设计,直至达至最优水准。

电源管理和效率

在DDR3设计过程中,电源管理尤为重要,其中高效的电源分配网络设计对降低功耗至关重要。此项工作需要细致挑选适宜的电源滤波电容及磁珠,并对电源走线进行合理布局。每个环节均会直接影响到系统整体的功耗与稳定性。

在电源设计中,我高度重视电源轨道的稳定性。鉴于DDR3所需电压低且受电源噪声和波动影响大,故采用多级别滤波与去耦技术维护电源轨的纯正及稳定。在这过程中,我得以学会平衡设计的精密与性价比。

热管理和散热设计

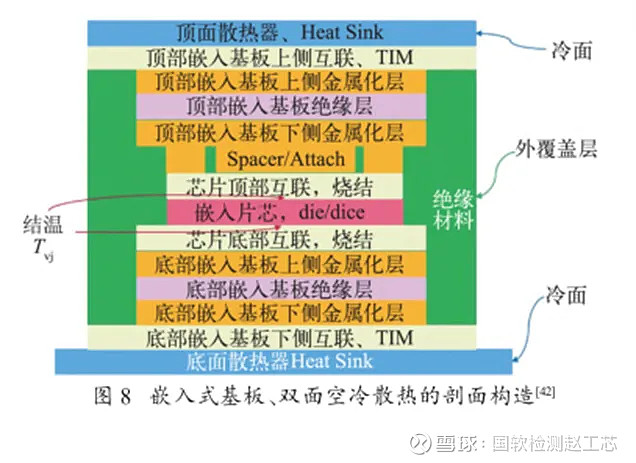

在DDR3设计阶段,需要充分考虑其散热问题,以保证其在高效运行时维持适宜温度。对此,我们采取了优化散热片与风道设计等措施,显著提高散热效能。

优化散热系统既是技术上的考验,亦是美学的实践。我需寻觅最优热流道,使热量顺利自发热元件传输至散热器。这并非单纯的散热片增设,更需全面考量材料挑选、布局规划及系统整体热力学效果。

测试和验证的重要性

在研发DDR3之后,进行一系列测试及验证以确保其性能与可靠性至关重要。我运用了多种测试工具和技术,如信号完整性测试、时序测试以及环境压力测试等。每次测试都对设计提出了挑战,同时也对我个人的专业知识和技能进行了检验。

在测试过程中,时常会遇到一些意料之外的问题,其原因可能在于物料选用不当、加工误差或者设计疏漏等方面。对此,我需迅速做出反应,深入剖析问题根源,并提出相应的解决策略。尽管这一过程充满挑战,却有效提高了我的问题处理能力。

持续学习和适应新技术

电子工程领域瞬息万变,新技术、新标准层出不穷。在DDR3设计过程中,我深感持续学习之必要。对待新型设计工具、材料与测试手法,需保持求知欲,持续掌握新知,应对行业变革。

在此过程中,我从实践中习得了团队协作应对挑战之术。每个项目皆非独立存在,方方面面的知识技能协同发挥至关重要。通过与同仁间频繁交谈、紧密协作,我不仅个人专业素养得以提高,更为团队贡献力量有了更深理解。

总结与展望

在DDR3硬件设计领域经历的旅程,每一次迭代都是全新的学术探求与实践指导。这些过程使我积累了丰富的实战经验以及专业知识,同时也深刻体验到设计过程中的乐趣与挑战。伴随着科技日新月异的发展,未来的内存技术将承载着更多创新特性并迎来新的挑战。期待在未来的设计阶段,我能继续发扬探索精神,以我所学,回馈电气工程领域的繁荣发展。

在此,我恳请各位专业人士参与并共享讨论,了解你们所面临的设计难题以及应对策略。同时,您的点赞及分享将帮助更多同行从中获益。期待各位的精彩分享!