电脑如同生活中的超能者,其核心部件DDR4内存,迅捷且强劲。然而,您是否了解,在面临断电危机之际,它们正与时间展开一场惊心动魄的赛跑。今日,笔者将揭示DDR4内存断电顺序的神秘面纱,带领大家感受这场关于时间与能源的紧张对决。

第一节:掉电,不只是没了电那么简单

请设想您正使用电脑进行关键任务操作,然瞬间,屏幕熄灭,所有活动全部终止。这并非仅因电力中断所致,对DDR4内存而言,这无疑将引发严重故障。所谓掉电时序,即在此类紧急状况下,内存必须严格遵循以确保数据不被瞬息间抹去的规范流程。

首要之事,掉电时序需内存模块在断电前完成数据存储,犹如暴风雨来袭之际,农人须急速收获所有农作物。若有拖延,恐会导致数据遗失,对依赖电脑操作者堪称灾难性损失。

第二节:时序的魔法:如何优雅地告别电力

“秩序”乃世间至美之境。以DDR4内存而言,其掉电瞬间的优雅源于严苛的时序掌控。内存模块须于电源关断之际,依序将数据妥善保存在非易失性存储器内。此过程犹如精心设计之舞步,每个动作皆需精确无误。

此等时序控制的繁复性堪比交响乐演出指导过程,信号与数据的准确传输与生成需在严格时间内进行。若有丝毫疏忽,皆可能引发体系性的崩塌。故而设计DDR4内存者,犹如舞台上的指挥家,他们的每一项抉择皆举足轻重。

第三节:掉电保护:内存的护身符

面临突然断电危境,DDR4内存所需之安全保障即为掉电保护功能。此保护机制能应对突发电源断供现象,从根本上确保内存数据得以保存。犹如英勇骑士,誓死保卫珍贵数据免遭损毁。

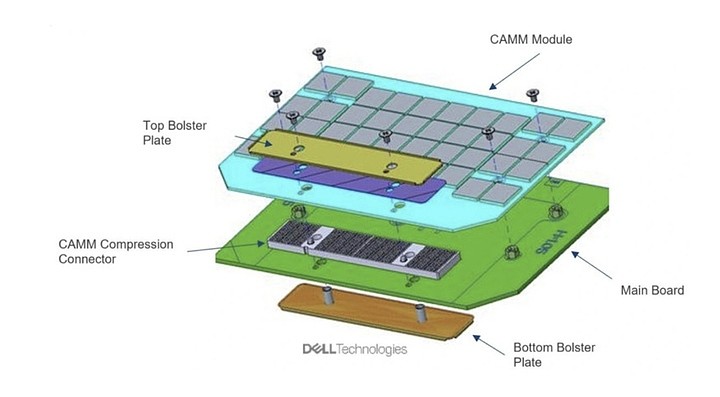

电源断电防护,主要依赖于电容为内存进行短期供电保障,使得记忆体能从容完成数据保存任务。犹如英勇士兵甘愿舍身护航友军撤退,这种大公无私的奉献精神,恰恰体现了DDR4内存电源断电保护机制所蕴含的核心价值观。

第四节:时序要求与数据完整性的关系

在DDR4内存领域,时序与数据完整性的紧密关联不容忽视。严谨的时序规定能确保数据断电后依然完整如初,仿佛建筑工程中的精确依图施工以保建筑稳定牢固。

DDR4内存的时序标准犹如护航神器般的存在,对所有依赖内存读取数据的操作都有着深远影响。不论是科研工作中的数学运算,亦或是日常操作里的文本保存,数据的丢失都有可能带来无法预估的损失。因此,DDR4内存的时序要求在确保数据安全性上起到了关键作用。

第五节:工程师的挑战:如何设计完美的掉电时序

DDR4内存研发团队在维持高性能下打造理想掉电时序上无疑遭遇了重大挑战,唯有兼具精湛科技知识和创新思维才能成功实现。

他们应如同探寻新星的天文学家,持续研究与实践,方能找出最优的时序方案。每个圆满实现的时序设计均是工程师才智与辛劳的见证,无疑应得到我们的赞誉。

第六节:用户体验:掉电时序对我们的影响

在日常电脑操作中,人们可能忽视了掉电时序的影响力。然而,正是这细微之处对保护数据安全起着关键作用。

在享用电脑技术便利之际,铭记设计断电顺序环节的工程师们功绩无疑至关重要。这些工作者成就虽未引起广泛关注,却实际构筑了我们不可或缺的数字世界。

第七节:未来的展望:DDR4掉电时序的进化

随科技进步,DDR4掉电周期亦日益严苛。预见之未来,或将呈现更智能化、高效化的断电防护系统。

这项进步展现了人类智慧,它不仅是技术的飞跃,更为数字世界注入稳定力量。我们期待,未来DDR4内存的掉电时序将攀升至新高峰,确保我们数字生活的稳固基石。

第八节:结语:在时间的长河中守护数据的安全

每一段数据,皆为时间之河的珍贵珠宝。DDR4内存守卫着这些珍宝,其断电时序如同坚不可摧的大坝,默默地保护它们不受损。

向不懈坚守岗位的工程师表示崇高的敬意,他们的辛劳使得我们的数字生活更趋于安全与美好。在此之际,请允许我向各位读者提问:您生活中的哪一些普通至极的科技或者设计,其实无时无刻不在无声无息地护卫着您呢?欢迎在评论区分享您的经历,让我们共同探讨,共同赞美,共享这一份智慧的珍贵果实。