尊敬的朋友们,今日我们将探讨一项看似深奥却紧密关联我们生活的主题——DDR5信号完整性。您可能并未意识到,DDR5内存条对我们计算机系统具有至关重要的地位,它肩负着迅速且准确地输送数据的重任。然而,倘若信号传输过程出现瑕疵,后果将不堪设想。信号完整性的核心便在于保证数据信号能够安全无误地由起点抵达终点,既没有遗漏,也不会被扰乱或失真。

试想下,如果您手中的手机信号时而畅通无阻,时而中断频发,通话过程中屡屡受挫,是否令您心烦意乱呢?DDR5信号完整性的原理正是为了防止这类状况在计算机设备中发生,以保证数据传输的稳定性和流畅性,如同高速公路上列车的运行状',秩序井然且不失高效。

DDR5的特点,为什么信号完整性这么重要?

DDR5内存相比其前代DDR4具备显著优势,速度更快、频率更高、容量更大且能效更优。这使得其能够应对更多数据量和复杂程序的运行需求。然而,高速传输同样带来了新问题,如信号干扰、延迟及失真的增加。若信号完整性不佳,这些高速数据很可能出现混乱无序的状况,如被风吹散的流沙。

如同在喧嚣派对中难以辨识好友语音,受制于过大的环境声音,数据通信可能会因干扰而产生错误;类似地,倘若DDR5在超速传输过程中遭受干扰,那么这将直接影响电脑的整体运行效能。

信号干扰,DDR5的隐形杀手

DDR5内存条面临信号干扰困扰,这一点不可轻视。试想身处繁闹咖啡厅环境中,周边嘈杂声音与时而中断的手机信号同样令人烦恼。与此类似的,DDR5内存条亦受制于电源线、其他组件乃至电磁波等因素对高速数据信号产生的影响。

此类干扰可能引发信号畸变、信息传输失误乃至整个系统瘫痪。因此工程师们需采用诸如使用屏蔽材质及优化线路布局等手段,以减轻干扰,保证信号的完整性与稳定性。

布线设计,让信号走得更顺畅

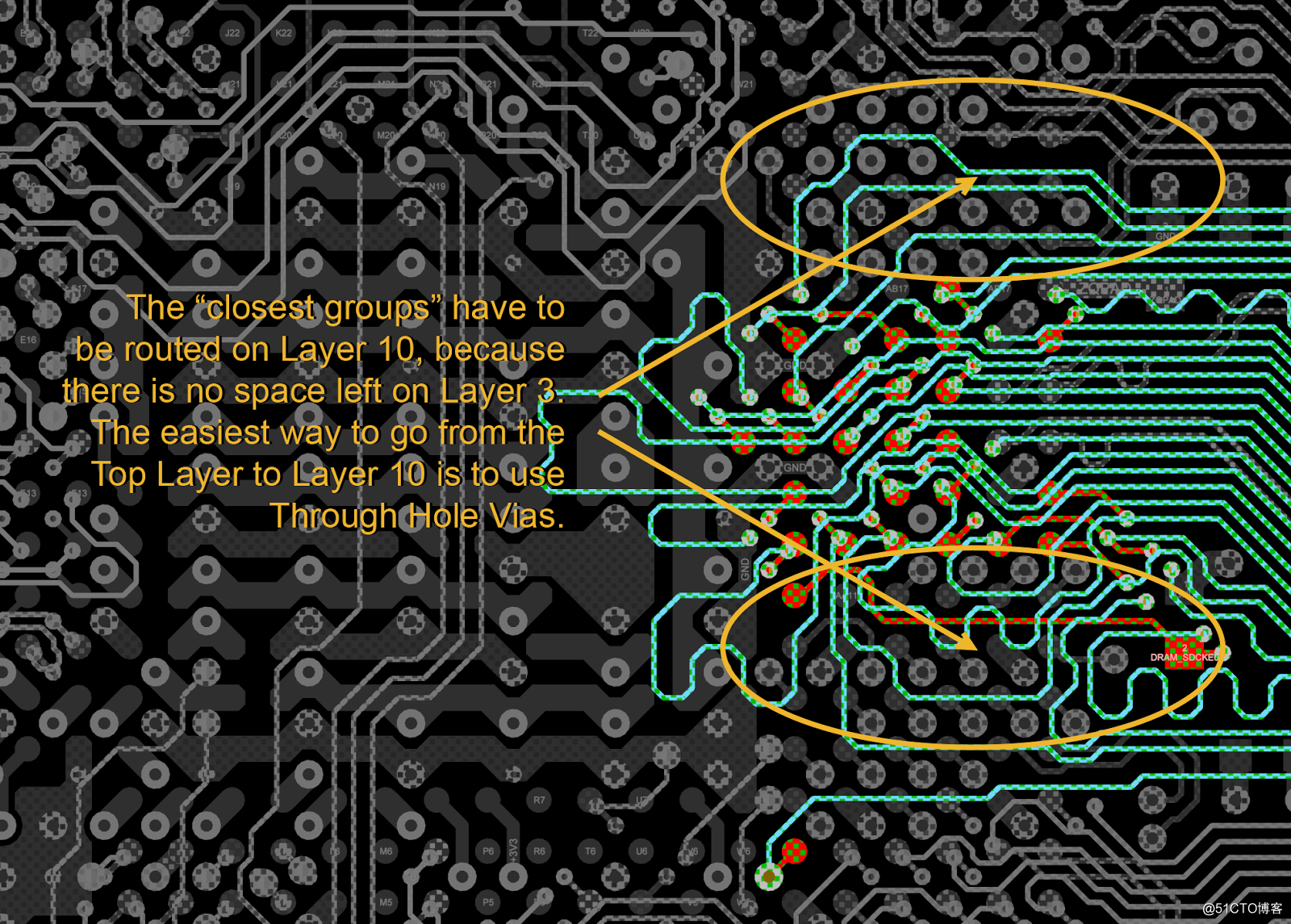

布线设计对保证DDR5信号的完整性至关重要。如同城市的道路规划,若不合理便导致交通堵塞。对于DDR5内存模块来说,布线设计的主要任务是使信号路径清晰简明,有效降低信号反射与串扰。

工程师们运用差分信号系统,犹如双通道高速公路般同时传送两路信号,进行有效校验以保证数据精准无误;其次,他们引进阻抗匹配技术,宛如为信号线路配备适宜之鞋履,进一步提速加固信号传送效果。

阻抗匹配,信号的合脚鞋

阻抗匹配看似空泛,实则关乎DDR5信号的保真度。试想,若足上无合适之鞋,行走定不安稳,甚至可能跌跤。同理,若信号线上阻抗无法吻合,信号流通必受影响,导致讯号发生改变。

工程师精密调整信号线路阻抗,使之与信号源及接收端阻抗相匹。如此,信号犹如穿合适跑鞋的健儿,自由自在奔驰于数据的高速路。

信号完整性测试,确保万无一失

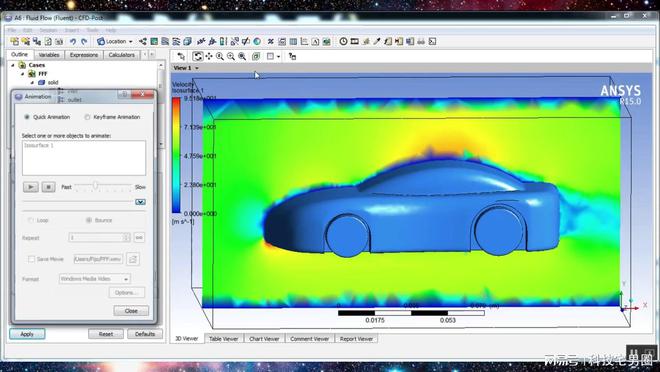

当DDR5内存条设计完成需进行繁琐严谨的信号完整性检测仿真,犹如产品上市前必备之质量审查,旨在使所有参数均满足行业标准。此流程中,工程专家运用各种先进仪器与软件,尽可能还原真实使用环境,对信号稳定度、传输延迟及失真现象进行精密检视。

若测试揭露潜在问题,工程师将依据检测结果实施相应调整及优化措施,直至信号完整性臻于至善。如此,我们即可安心利用DDR5内存条,尽享其所提供的快捷数据传输之美。

未来展望,DDR5信号完整性的挑战与机遇

随着科技日新月异发展,DDR5面临的信号完整性课题愈发艰巨。频率与内存容量的提升为之带来更为繁复的信息调度问题。然而,与此同时,这亦催生了诸多崭新机会,例如尖端信号处理手法和智能化布线设计方案等。

工程师正致力于研究新科技如强化信号传输与运用人工智能降低信号干扰的能力。此举或有助于实现对DDR5信号完整性的重大提升,进一步提高数据传输效率及稳定性。

结语:让数据流动更顺畅的大冒险

总而言之,DDR5信号完整性的重要性在于为计算机系统提供高效稳定的运行环境。由此影响范围涉及信号干扰控制、布线规则设定及阻抗匹配调整等诸多关键环节。在此基础上,随着科技持续发展,人们对DDR5信号完整性能期待着更多可能的创新与突破。

请问各位,对未来DDR5信号完整性技术发展的展望里,您认为哪项革新最可能引发重要飞跃?请在评论区畅谈见解,记得点赞与分享。