尊敬的各位,我是电子科技领域的探索者阿强。在今日的分享中,我们将共同探究DDR3内存中的各种信号线路。这些平凡而又独特的线条,隐藏了无数未知的奥秘。现在,请您跟随我的脚步,开启这趟神奇之旅!

DDR3信号线的基本概念

首先,我们需明确DDR3定义为何物。简言之,DDR3为一种高速且节电的存取单元技术,其成功秘诀在于众多信号线条的协同作用,犹如DDR3之"心脏与灵魂",缺之不可。

DDR3的信号线,其职责并非平淡无奇。每条线均担负着传输数据、控制指令以及时钟信号等多重使命。试想,这些信号线宛如快递员,以迅疾且精准的方式将重要信息(数据)传送至目的地。

DDR3的主要信号线种类

首先,我们来探讨DDR3几个主要信号线包括哪些内容。其中首要者当属数据线,其数量众多且至关重要,负责传送真实的数据量,使您得以畅快地进行游戏、观看视频以及其他各类精彩活动。

接着是地址线,帮助DRAM芯片定位存储单元的位置或提取读出数据。若失去这部分功能,数据将陷入如同无头苍蝇般的混乱状态。

此外,还存在控制线上,此类线路承载了诸如启动读取、启动写入或刷新内存等多种指令传输工作。其角色犹如交通管制员,借助有序的数据流来实现信息管理。

数据线的秘密

看似简陋的数据线实则是DDR3芯片内最为精密的组件。每条数据通路如同快速且稳定的高速公路,协调着高速驰骋的数据汽车顺利通行。

DDR3的数据传输线路常使用8位或16位规格,换言之每次可处理8位或16位信息。然而,DDR3具备双通道技术特性,使其实际数据传输效率提升至两倍。设想一下,如同两条并列的高速公路输送数据,大幅提高了工作效率。

地址线的作用

尽管看似平淡无奇,地址线对于内存芯片而言却负荷着至关重要的使命。它指示了数据正确存储或提取的位置,如同为每一份数据包裹粘贴上明确的地址标签,以确保其精准送达目的地。

DDR3内存地址线数目与内存容量及组织结构相关。通常将其分为行地址和列地址两部分,以便更有效地处理存储区内数据。行地址选定位所对应的较大存储区域;列地址在该区域中精确定位。此分层架构为存储器管理提供了更为有序且高效的途径。

控制线的魔力

控制引脚如同DDR3之核心,调度各类指令,维系系统顺畅运作。具体包括读、写、刷等关键指令。若无此类指令,DDR3犹如盲目驾驶汽车,虽有动力,而无法实现目标。

控制线路的数量与种类视乎DDR3设计及性能而定。常见的基础管理线路包括芯片选定、读取/写入及刷新操作,诸如此类犹如精密的操控阀门,对内存芯片的各项操作进行精确控制。

时钟信号的重要性

除电缆外,DDR3还设有地址信道及控制信道,而其最核心的一根信号线便是时钟信号线。此线犹如DDR3的脉搏,掌控着所有数据传输的节律与时机。

严格执行时钟信号线路,确保所有数据交换均依据稳定的时钟脉冲进行同步,从而保证准确无误地读取和写入数据,避免信息遗失或误传。

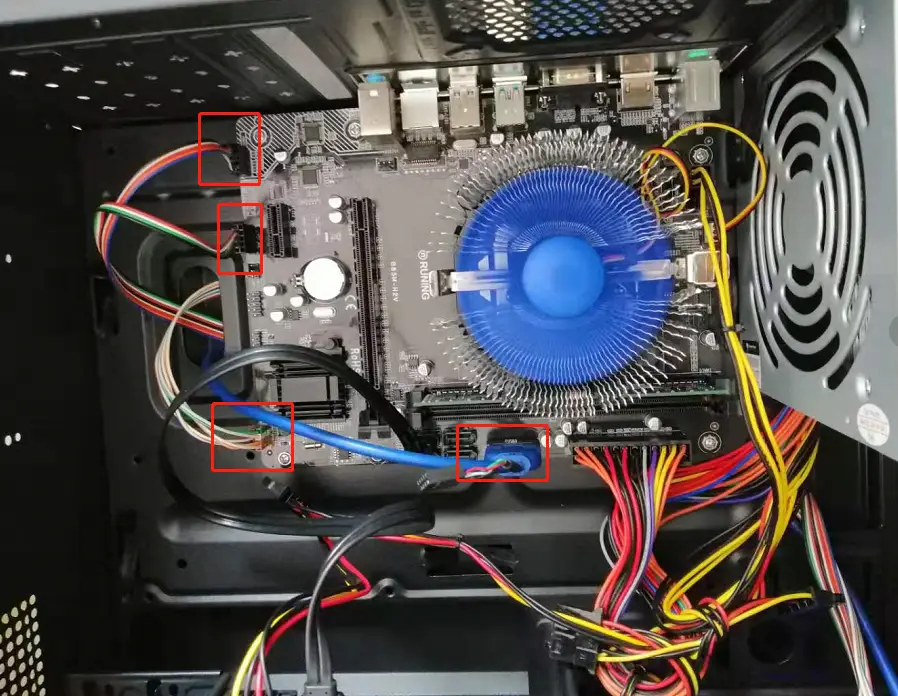

信号线的布局和设计

在优化的DDR3设计中,信号线的合理分布起着关键性作用。这种设计方法能减小信号干扰,从而提升数据传输速度及稳定性。此过程犹如对城市交通网络进行精巧布局,以降低通勤压力,从而提高运输效率。

工程师运用诸多尖端技术,如差分信号、串扰抑制等手段,对DDR3信号线布局进行了精细调整。这些先进策略犹如一套先进交通管理方案,致力于保障数据传输的效率与安全性。

信号线的未来发展

最后,阐述一下DDR3信号线的未来趋势。伴随着科技的迅猛发展,未来的DDR3信号线将愈发地高效且智能化。有望融入更多功能元素,如自适应优化数据传输路径或实时监测数据传输状态等。

此系统犹如未来的高速公路,其不仅仅具备更高的运行速率,更为重要的是还搭载了智能交通调控系统,可自动化调整车流,以保证道路时刻保持流畅。这种高新技术将使DDR3性能得到进一步提升。

DDR3信号线路看似平实无奇,实则深刻诠释各线条各自精妙技术内蕴,赏心悦目的数据线、地址线、控制线和时钟信号线无不展示出研发工程师们匠心独运的智慧结晶。

在此,请允许我向各位提出一个深度思考题:您认为未来的存储科技将有何革新?其对我们的数字化生存方式将会带来怎样的影响?请在下方留言区畅所欲言,同时,别忘记为本文点赞并分享,让更多人领略到DDR3信令线路的无穷魅力!