DDRAvalon接口在电子工程领域扮演着至关重要的角色。这种接口主要被用于将DDR内存与控制器等配件相连接。它的性能和特性对整个系统的存储性能具有决定性的影响。

基本原理

ddravalon接口在数据传输上拥有独特机制。该机制通过一系列信号协议确保数据在DDR内存与控制器间准确快速传输。比如,它利用特定时钟信号同步传输过程;若时钟信号出错或偏差,便会引发传输错误。在通信基站等设备中,对数据传输的准确性要求极高,ddravalon接口的此特性需精心调整。此外,其数据读写规则亦基于此原理,通过不同指令处理不同读写需求。

这种接口的基本原理涵盖了命令解码等多个环节。当控制器发送读写指令,ddravalon接口便会迅速解码该指令,明确是读取还是写入特定地址的数据。整个过程耗时极短,确保了系统的运行效率。

性能特点

在性能上,ddravalon接口展现出高带宽的显著优势。这种接口能在短时间内传输大量数据,完美契合众多系统对海量数据快速处理的需求。以大型数据中心的服务器为例,面对用户对数据的频繁请求,高带宽的ddravalon接口便能发挥出巨大作用。

同时,其低延迟的特性不容小觑。低延迟意味着数据传输速度加快,能够迅速抵达目标。在实时性要求极高的场景中,比如某些高速自动化生产线的控制系统里,低延迟的ddravalon接口能确保设备迅速接收并处理数据,进而使生产线运作更加高效。

与其他接口对比

与传统的内存接口不同,ddrAvalon接口的特点十分鲜明。在带宽方面,传统接口的带宽通常无法与ddrAvalon接口相提并论。尤其是在处理复杂的多媒体数据或大量网络数据时,传统接口往往显得力不从心。而ddrAvalon接口凭借其高带宽,轻松应对这些挑战。

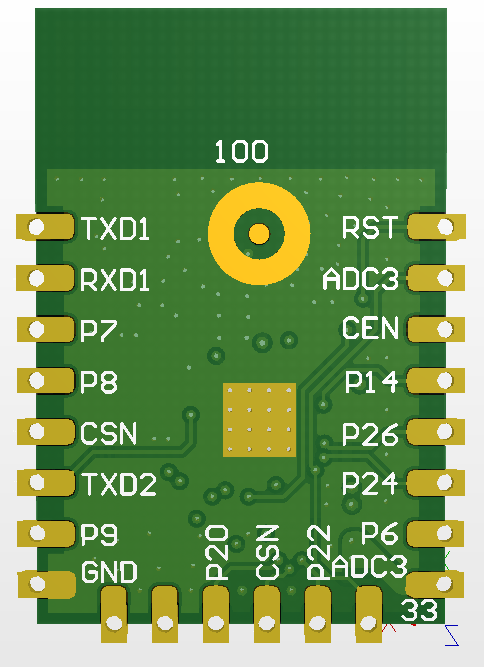

在兼容性方面,ddravalon接口主要服务于特定的系统架构,不过在这些架构中,它的兼容性表现相当不错。以某些使用特定FPGA的设备为例,ddravalon接口能够与之良好匹配。相较之下,其他接口可能面临兼容难题,进而可能引发系统不稳定或性能降低的问题。

设计考量

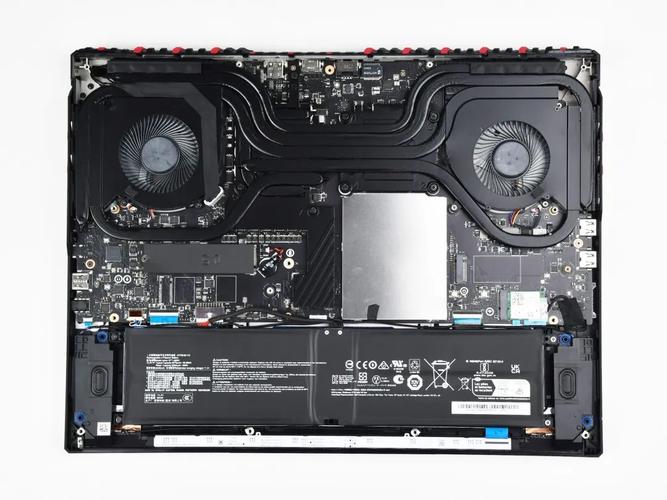

在电路设计领域,布局布线是关键所在。ddravalon接口的数据传输速度极快,对信号的完整性有着极高的要求。因此,在进行布局布线时,必须尽量降低信号的干扰和衰减。这就要求我们合理规划信号线的路径,避免出现交叉等不良情况。

电源管理是设计过程中不可或缺的一环。稳定的电源对于ddravalon接口的正常运作极为关键。电源不稳定可能会引起信号波动,进而导致数据传输出错。在便携式设备中,必须细致设计电源管理模块,以确保ddravalon接口能够持续稳定地工作。

调试过程

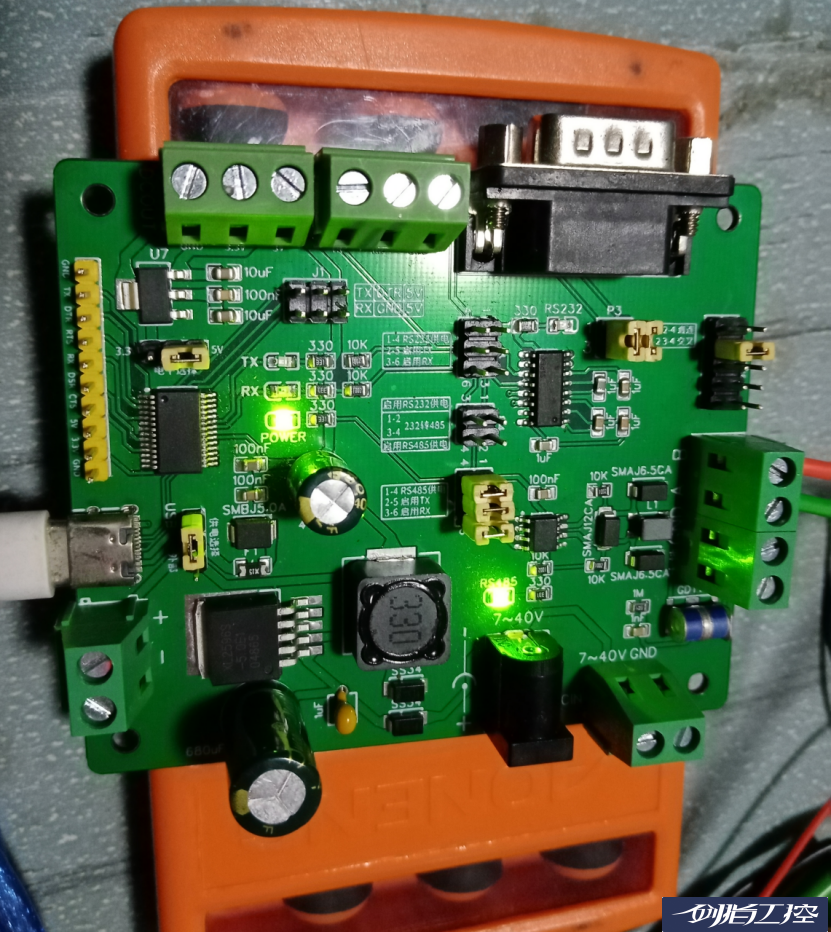

调试ddravalon接口时,信号检测至关重要。我们必须用专业设备来检查接口的信号是否正常,比如时钟信号的频率和稳定性,以及数据信号的准确性。一旦发现异常信号,就必须迅速找出问题所在并予以解决。

参数配置对于调试至关重要。需根据具体应用场景准确设定接口的各项参数,如数据传输速率等。若参数设置有误,将直接影响系统性能。以新开发的嵌入式系统为例,若参数配置不当,可能导致数据传输缓慢,甚至引发系统崩溃。

未来趋势

技术不断进步,ddravalon接口的速度和带宽自然也会随之提高。这样的提升将有助于满足未来对数据处理能力的更高要求。比如在人工智能和物联网这些新兴领域,快速的数据交换至关重要。只要ddravalon接口的性能持续增强,就能为这些领域提供更加强有力的支持。

然而,我们也遇到了兼容性的难题。随着未来设备可能运用更多新颖的技术和架构,如何确保ddravalon接口能够与之顺畅配合,这成为了厂商和工程师们必须提前深入思考的问题。

我想请教大家一个问题:你们觉得ddravalon接口将来会在哪些新兴领域展现出其独特的价值?欢迎各位留言、点赞和转发这篇文章。