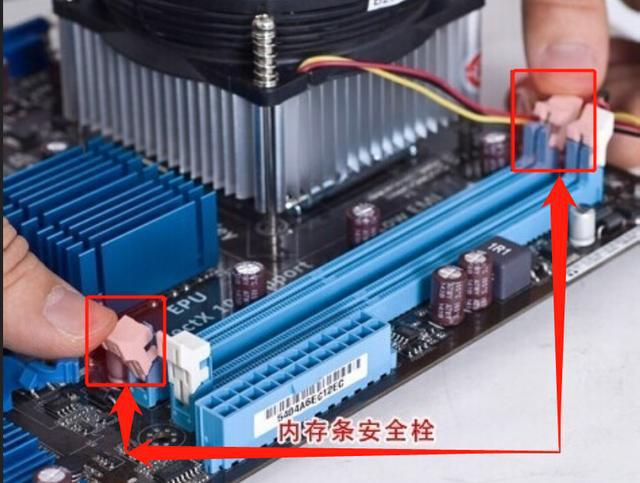

DDR模块图,即双倍数据率模块图,是深入理解DDR存储系统运作机制的关键。图中包含地址线、数据线、控制线等多种元素,它们协同工作,确保数据的高速读写。在计算机硬件领域,DDR模块图占据着极其重要的位置。无论是电脑、服务器还是其他电子设备,只要涉及数据存储,就很可能与DDR模块图有所关联。

地址线的作用

DDR模块图中,地址线扮演着至关重要的角色。凭借特定的地址编码,它能够精确地锁定存储阵列中的某个特定存储单元。这就像精准的导航,指引数据检索的方向。比如,在广阔的内存空间中,若没有精确的地址指引,寻找所需数据便如同大海捞针。地址线如同桥梁,构筑起系统与存储单元之间的连接路径。此外,地址线的位数直接影响到可寻址的范围,因此与内存容量的扩展密切相关。

地址线的布线设计同样不容忽视。合理的布线设计可以降低信号干扰,增强数据传输的精确度。若布局不合理,则可能造成信号传输失误,进而引发数据混乱等一系列问题。

数据线传输数据

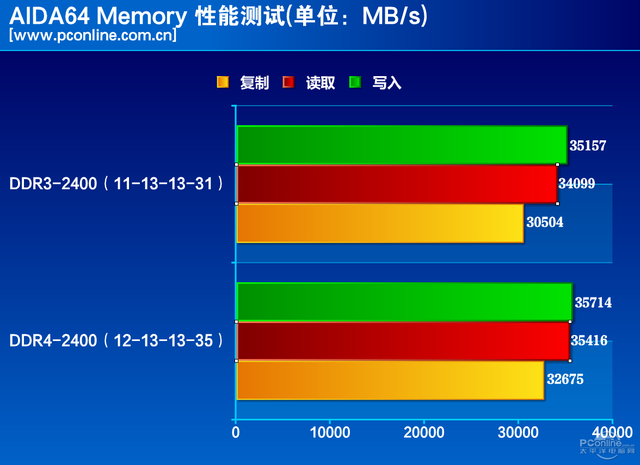

数据线承担着实际的数据传输任务。它的宽度直接影响到一次传输数据的数量。宽度越宽,传输的数据量自然就越大。这样的设计对于提高数据传输的整体速度大有裨益。这就像一辆宽体卡车比窄体卡车能装载更多货物一样,道理相通。

数据线的读写操作颇为复杂。在读取或写入数据时,必须严格遵守严苛的时序规范。任何微小的时序偏差都可能导致数据传输失败,或者引发数据错误。因此,必须采用极其精确的时序控制电路,以确保数据的准确性。

控制线的功能

控制线在DDR模块图中如同指挥家手中的指挥棒。它负责指挥整个模块的读写操作流程。就像芯片的选择信号,它能够决定哪个芯片将被激活,参与到数据交互的过程中。

不同的控制信号各司其职。比如时钟信号,它按照既定的频率为数据交互设定节奏。若时钟信号出现错误,就好比乐队失去了鼓点的指引,数据交互将陷入混乱。而确保控制线的准确控制,对于DDR的正常运行是至关重要的。

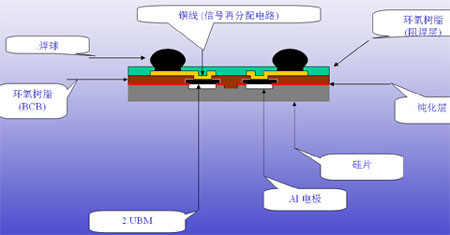

存储阵列的构造

存储阵列是DDR模块图中的关键部分。它由排列紧密的存储单元构成,形成一个矩阵。存储单元的布局方式直接关系到内存的性能。比如,为了实现快速读写,存储单元在阵列中的排列和分组都遵循特定的规则。

存储阵列的扩展方法同样至关重要。究竟是通过增加阵列的行数还是列数来增大存储空间,这需要综合考虑众多因素,例如生产成本、电路板空间等。这些因素无疑对DDR模块的设计产生了深远影响。

缓存结构的影响

DDR模块图中,缓存结构扮演着关键角色。缓存能够暂时存放那些频繁访问的数据,如此一来,访问存储阵列的频率就能显著降低,从而提高读取效率。若将存储阵列比喻为一个庞大的仓库,那么缓存就如同仓库旁的一个便捷的小储物间,存放着一些常用的物品,便于快速取用。

缓存的大小与管理的策略,对性能有着直接影响。选取合适的缓存尺寸,可以在成本与性能之间找到一个理想的平衡点。然而,若缓存的管理策略不当,可能会造成缓存利用率不高,进而造成缓存资源的浪费。

模块图的优化方向

对DDR模块图进行优化,可以增强DDR系统的整体性能。首先,电路布线是关键,通过优化布线,可以降低信号干扰,确保数据传输的稳定性。这就像对城市道路进行合理规划,以促进交通流畅。

此外,我们还可以在元件挑选及参数设置上寻求改进。挑选恰当的芯片等元件,并对这些元件的参数进行调整,如此一来,DDR模块的整体性能将得到显著提升。

我想请教一下,在您阅读DDR模块图的过程中,最大的难题是什么?若这篇文章对您有所裨益,不妨点个赞,或者将它分享出去。