DDR(双倍数据速率)的读写规则在计算机存储领域占据着至关重要的地位。这一规则决定了数据在DDR内存中的存储与读取方法,对内存的性能、效率以及与硬件组件的协同作用等多个关键方面有着直接影响。对于硬件开发者来说,理解DDR读写规则有助于优化设计;对于计算机维护人员而言,它有助于故障排查;而对于技术爱好者来说,则是深入研究系统性能的宝贵财富。

DDR读写的基础原理

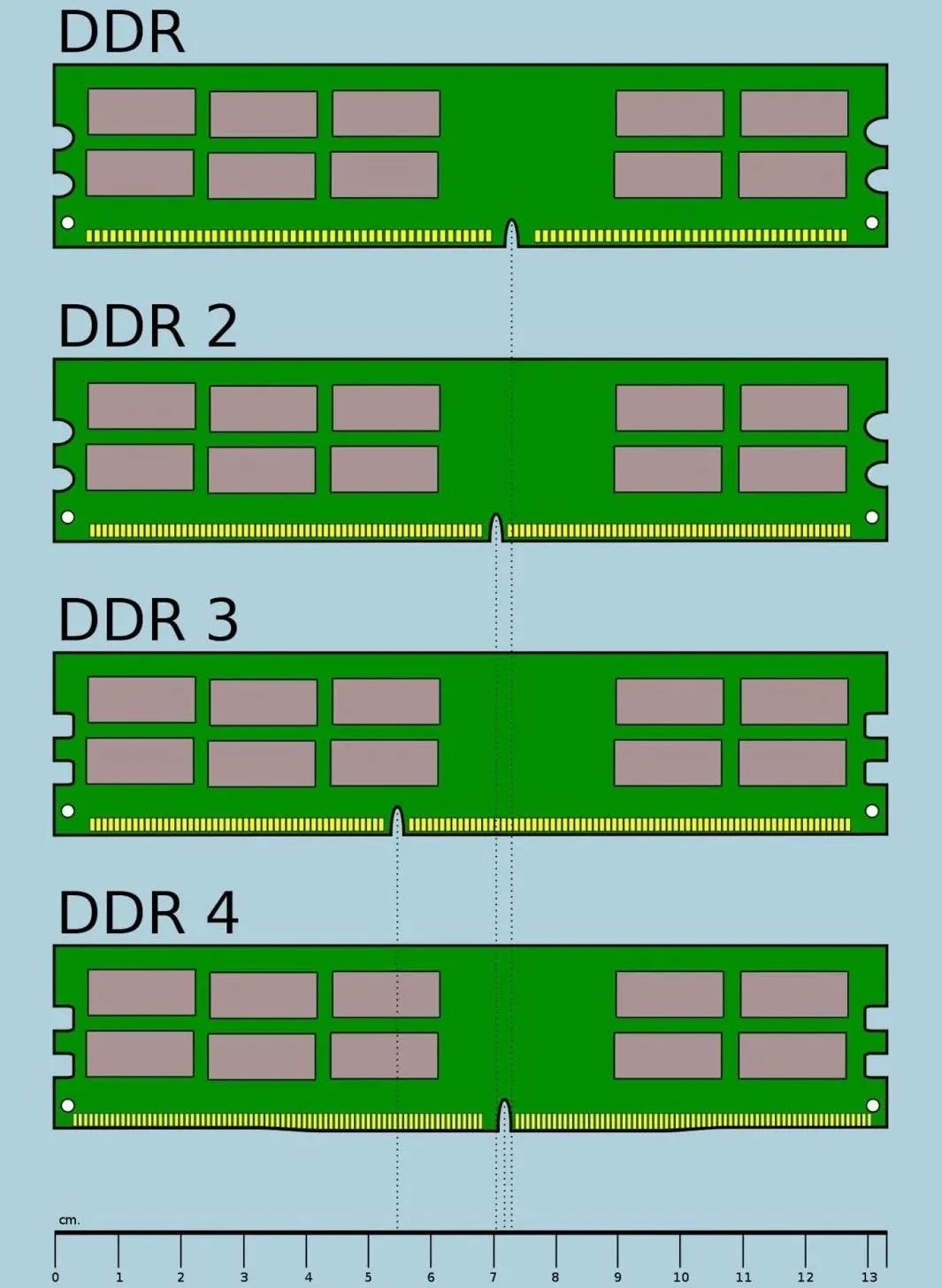

DDR的读写机制源自其内部构造,它能在时钟信号的上升和下降两个阶段进行数据传输,以此达到双倍的数据传输速度。这种操作背后有底层电路逻辑的支撑,相较于传统内存,这算是一种创新的数据传输方式。其工作原理还决定了在读写过程中对数据的处理顺序。此外,DDR的读写还与存储单元的排列方式紧密相关。众多存储单元协同作业,共同完成数据的读写任务。

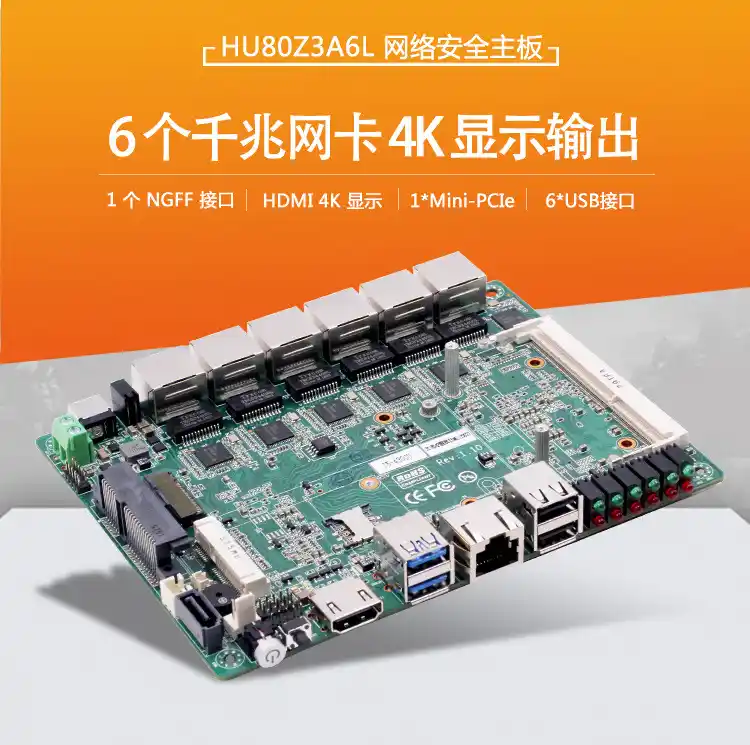

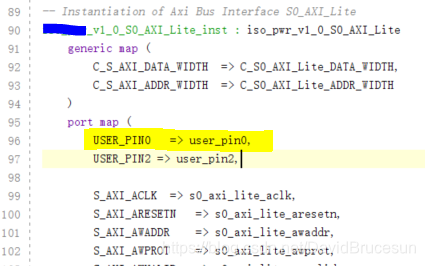

在实际的电路设计中,DDR的针脚布局是依照其读写机制来安排的。各个针脚各司其职,负责传输不同类型的数据、地址等关键信息。只有当这些针脚准确连接,并严格按照规范与时钟信号同步,DDR的读写功能才能得以正常执行。若针脚连接出现差错,或是信号时序配合不当,便可能引发读写错误,甚至导致数据丢失。

读写的时钟信号作用

在DDR的读写过程中,时钟信号扮演着指挥官的角色。它的频率直接影响了数据传输的速度。每个时钟周期,都像是操作的一个节拍,正是在这个节拍中,数据的读写得以完成。时钟频率越高,单位时间内数据传输的机会也就越多。

时钟信号必须保持高度稳定,任何微小的抖动都可能引发读写错误。DDR的读写操作必须精确地依据时钟周期的上升和下降沿执行。比如,如果在数据读写的关键时刻发生极小的时钟抖动,数据读取或写入就可能出错,这对系统的准确读取和存储造成严重影响。

地址传输与数据定位

地址传输,作为DDR读写规则的关键环节,至关重要。它清晰地标示了数据的物理存放位置。这就像邮编能够精确地将邮件投递到指定地址,只有传输正确的地址,才能确保我们能够准确找到所需读取或写入的数据存储点。

在进行数据写入过程中,DDR需先准确接收地址信息,随后将数据放置于相应的存储位置。至于读取数据,DDR同样依据传入的地址定位至对应的数据单元,并传输数据。地址的准确性对读写操作的可靠性极为关键,因此在设计计算机硬件系统时,确保准确传输地址是必须遵循的步骤。

数据的写入规则细节

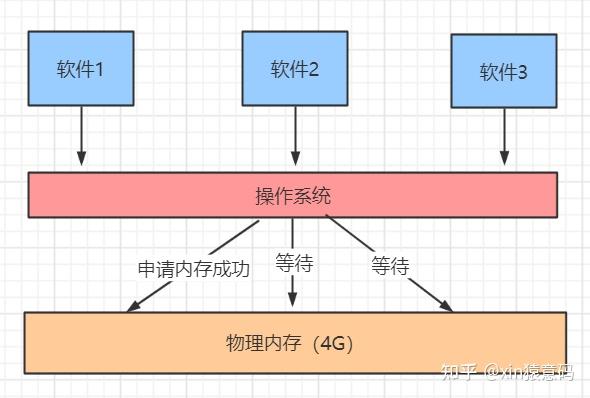

数据写入的规则中包含众多细节。在正式写入数据前,DDR内部需要完成一系列准备工作。比如,先要检查存储单元是否能够被写入。如果存储单元正在被读取,或者处于某种特殊保护状态,那么可能就无法进行写入操作了。

写入数据时需遵循特定宽度传输,这宽度通常固定,比如8位或16位,具体视DDR规格而定。此外,数据写入还需听从一系列命令信号的指引。比如,在发出写入命令前,必须满足一些前提条件,比如写入使能信号必须正常等。

数据读取过程从接收读取指令开始。这个指令会启动一系列的操作步骤。DDR芯片会依据接收到的提取地址信息,在其存储单元中寻找数据。找到数据后,它会按照既定的数据宽度进行读取。

数据在从DDR传输至其他设备时,必须依照特定的数据传输规则。这些规则旨在确保数据的完整无误。鉴于DDR输出的数据可能被多个设备共享,该规则对于确保系统准确获取DDR数据至关重要。

与主板和CPU的协同工作

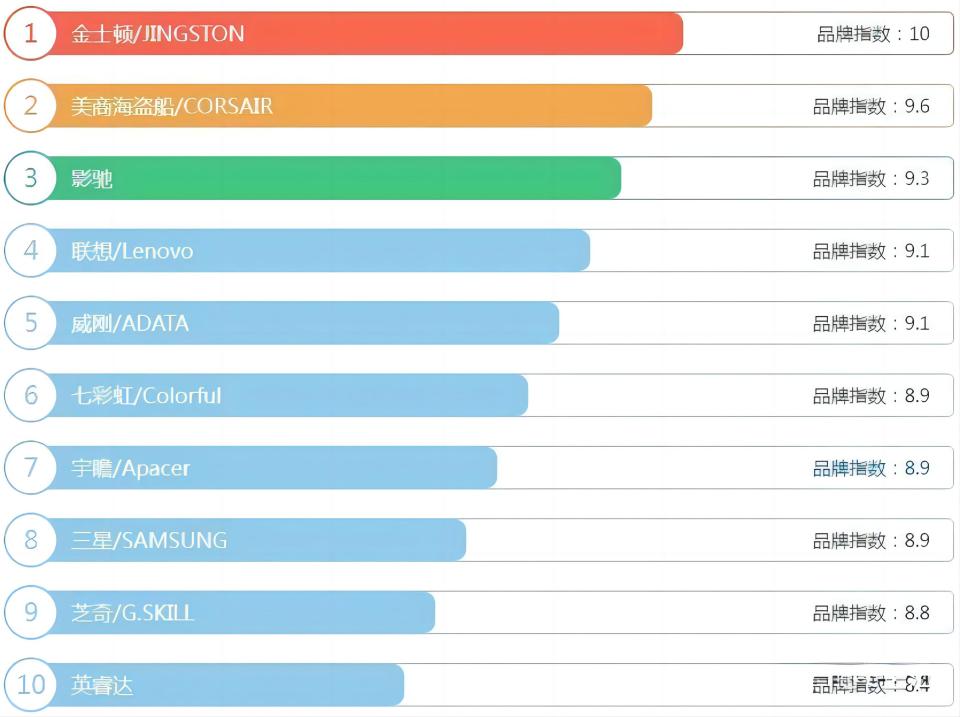

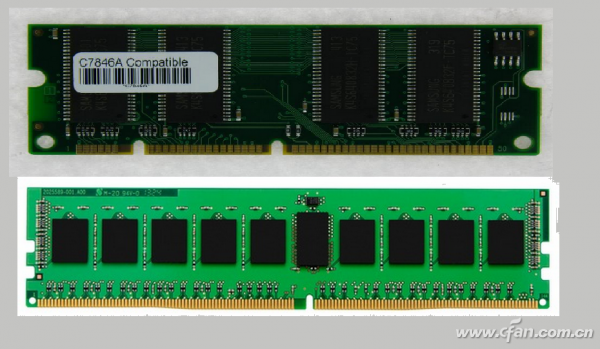

DDR与主板及CPU的协同作用,是决定计算机整体性能的关键因素。主板负责为DDR提供必要的物理连接和电气环境支持。DDR的读写时序必须与主板的时钟等部件相匹配。若主板电路设计对DDR支持不足,便可能引发读写不稳定等一系列问题。

CPU是DDR数据的关键控制器,负责发送读写指令等操作。CPU缓存的布局与DDR的性能密切相关。若CPU缓存未能与DDR有效配合,便会降低数据传输的效率。例如,当CPU急需从DDR快速读取大量数据时,若缓存未能提前做好预取等准备工作,数据传输便会延迟。

在工作中或学习时,你是否遇到过因DDR读写规则不熟悉而引发的电脑故障?若有类似经历,欢迎在评论区留言分享。同时,也请你点赞并转发这篇文章。