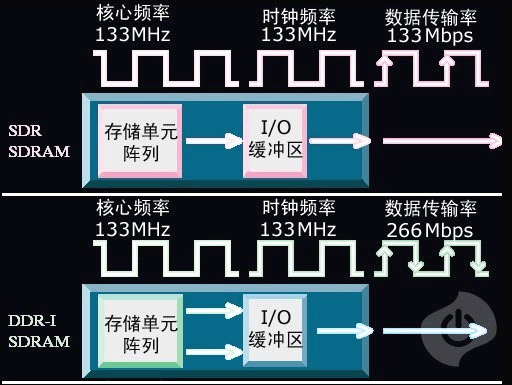

DDR(双倍数据速率)的保持时间在DDR存储技术领域至关重要。这实际上是指数据在传输过程中的稳定与精确。它对硬件电路设计及DDR内存模块的正常运作有着极其关键的作用。

保持时间的定义

保持时间的概念需先明确。这种时间,是指时钟信号触发后,数据必须维持稳定的最短时长。它相当于一个不容逾越的时间界限。在DDR的工作机制中,若保持时间设置不当,接收端的数据可能会出现错误。这绝非小事,因为哪怕是微小的误差,也可能导致数据传输链路整体失效。将数据传输比喻为火车在轨道上行驶,保持时间便是确保火车不脱轨的关键因素之一。它的确立并非偶然,而是基于DDR的存储原理,经过长期实验与精心设计,最终确定的一个具体时间数值。

电路设计中,时间参数至关重要。设计师在设计的每个阶段,都必须对这一参数进行精确测量与调整。若在这一过程中出现误差,将直接影响产品质量,甚至可能导致DDR设备无法正常运行。

保持时间与时钟的关系

DDR系统运作的关键要素之一是时钟信号,它与时间的维持紧密相关。时钟信号负责精确地安排数据的读写操作。时间维持是时钟信号体系中的一个关键环节。观察时钟的上升或下降沿,我们就能看到时间维持的重要性。从电路的视角出发,每当时钟信号产生脉冲,随之传输的数据必须在规定的保持时间内保持稳定。

时钟如同指挥家,数据则是演奏者。指挥家一旦发出指令,演奏者便需在规定的时间内作出响应。若两者配合失谐,原本和谐的音乐会沦为刺耳的杂音。在DDR系统中,若时钟与保持时间的协调出现问题,便会导致数据读取与写入失误,进而干扰系统的稳定运行。

保持时间与数据跨异步时钟域传输

DDR系统中,数据传输往往需要跨越不同的异步时钟域。这时,保持时间就像桥梁的支撑点至关重要。跨异步时钟域传输会导致时钟频率和相位发生变化。因此,保持时间至关重要,它能确保数据在这样不稳定的传输环境中不会出现乱序或错误。

在复杂的电脑主板设计中,不同模块可能采用不同的时钟源。当DDR内存与处理器等设备交换数据时,就出现了跨越异步时钟域的问题。若未妥善处理时间同步,数据在传输过程中可能会出错,就如同信件在邮寄途中丢失或内容被篡改一般。这种情况下,电脑系统可能会出现各种难以解释的故障,例如程序突然崩溃,电脑无缘无故重启等。

如何检测保持时间是否正确

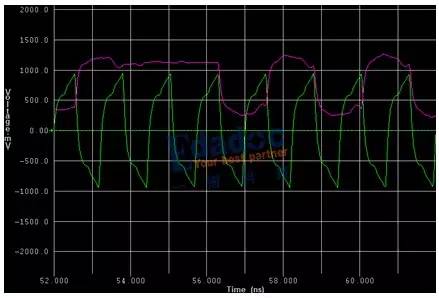

确保检测保持时间的准确性至关重要。通常,我们会采用示波器对信号进行测量。示波器能捕捉到时钟信号及数据信号,随后通过精确的测量和比较,以判断保持时间是否达标。这一过程相当细致,需要借助专业仪器,并且操作人员需具备熟练技能。

此外,还有专门的测试芯片或测试电路可供使用,用以检查电路设计。这些检测工具可集成至电路系统中,用于在系统运行前或运行中检测保持时间。这好比盖房子时使用的质量检测工具,确保每个环节的质量达标。若未能准确检测保持时间是否准确,就如同盖房子时忽略了房屋根基的稳固性,后续隐患将无法估量。

保持时间故障的影响

时间一旦出现故障,后果不堪设想。最直接的影响是数据的丢失和错误。尤其在DDR内存中,若写入数据时保持时间出现问题,错误数据便可能被存入内存。等到读取数据时,获取到的也是错误的信息。这种错误对于金融数据处理、医疗影像数据存储等对数据准确性要求极高的领域来说,是无法容忍的。

此外,此类故障甚至可能引发系统全面瘫痪。以运行大型数据库的服务器为例,DDR内存是数据库读写不可或缺的核心部件。一旦出现时间同步故障,服务器可能瞬间停止工作,对企业造成严重损失。例如,在电商企业购物高峰期,服务中断可能导致大量顾客流失。

保证保持时间准确性的策略

为确保时间精确度,首先在设计阶段需进行精确的计算。需依据DDR的工作频率、时钟特性等因素,运用严谨的公式计算出适宜的保持时间。制造过程中,需严格把控误差幅度。从电子元件的挑选到每一道生产工序,都必须依照高标准执行。

在DDR系统投入使用的测试阶段,必须进行彻底的测试。这不仅仅是对保持时间的单一参数进行检验,还需将其置于整个系统环境中,全面考量各种复杂情况,例如在高负载、长时间运行等状态下保持时间的稳定性。关于这一点,我想请教大家,在接触DDR相关设备或进行研究时,是否遇到过因保持时间问题引发的故障?期待大家能积极点赞并转发这篇文章,让更多人认识到这一关键概念。