DDR,即双倍数据率,在现代电子系统的设计中占据着至关重要的地位。这项设计旨在确保DDR内存能够准确且高效地运作,是一项涵盖众多复杂技术层面和广泛知识体系的系统性工程。

原理与概念

DDR验证设计,首先需弄懂DDR的工作原理。DDR技术允许在时钟的上升和下降沿进行数据传输。就内存架构而言,其行列地址以及存储单元的排列方式,对数据读写有着显著影响。以一个简单的DDR芯片为例,若地址映射缺乏明确规划,读写数据可能会出现混乱。而且,DDR对时序的要求极为严格,每个控制信号与数据信号之间的时序关系,都直接关系到系统的稳定性。比如,在读写操作中,CAS潜伏期的设定,就关系到数据读取的延迟时间。

深入理解这些概念,对于确保DDR验证的有效性极为关键。若对原理一知半解便开始验证,那便如同盲人摸象,很难全面保证系统的准确性。

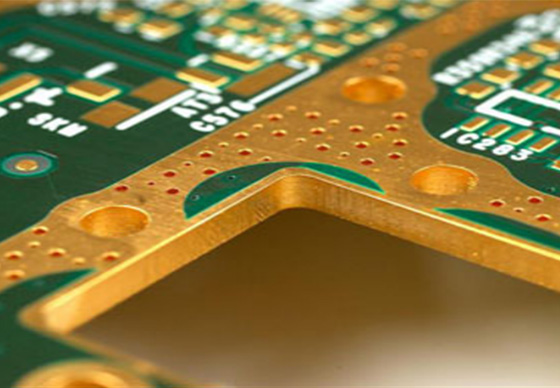

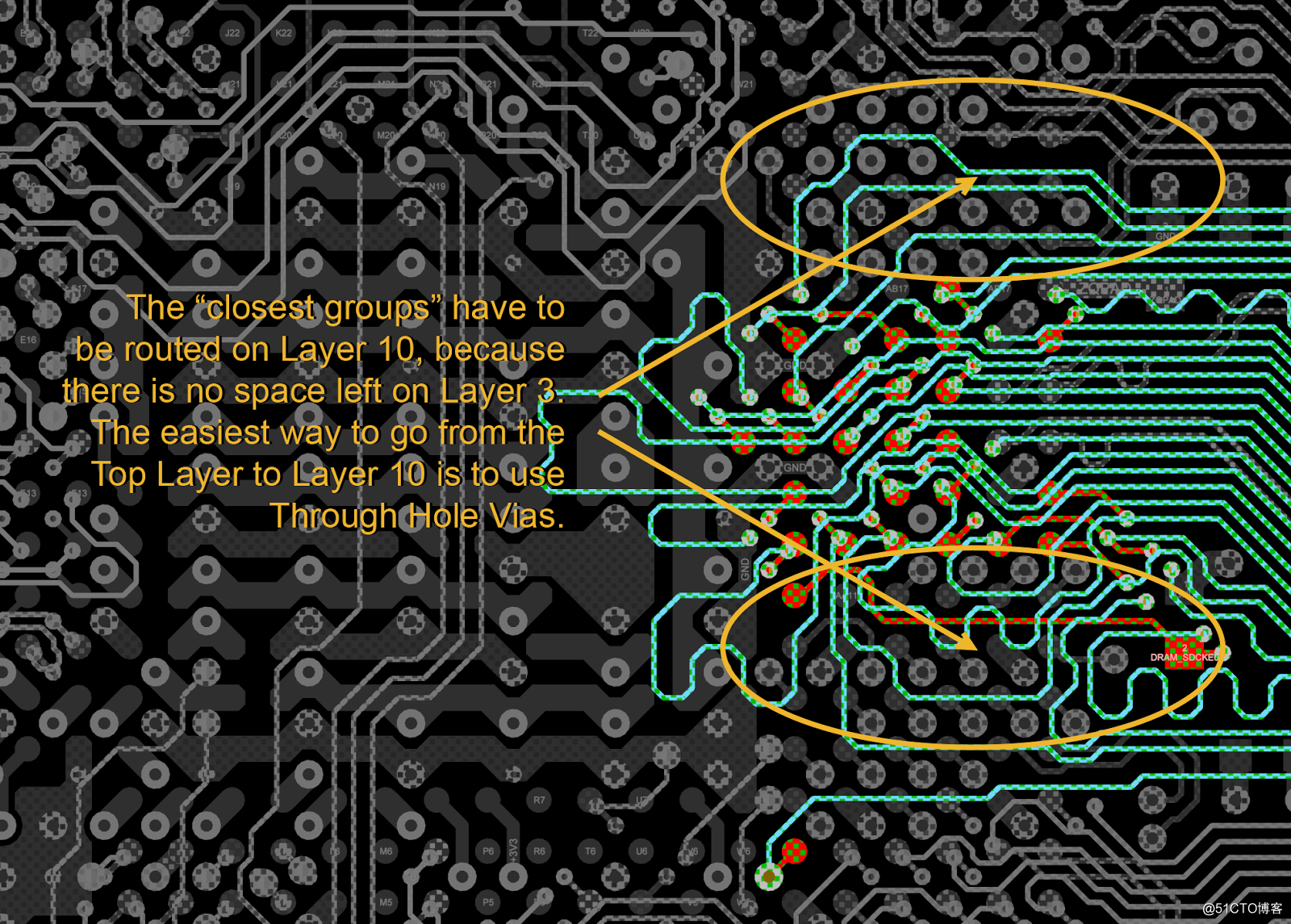

信号完整性对于DDR验证至关重要。首先,关键信号的布线长度至关重要。在DDR高速数据传输中,过长的布线会引起信号衰减和反射等问题。比如,数据信号从内存芯片传输到控制器时,若布线过长,信号到达时间的差异可能导致数据读写错误。其次,信号间的串扰同样不可忽视。相邻信号可能会相互干扰,处理不当会导致信号电平波动,影响数据准确性。尤其是在高密度电路板设计中,这一问题更为明显。

DDR验证设计人员务必充分重视信号完整性,否则很可能会遇到众多难以解决的难题。

测试用例设计

DDR验证过程中,设计出有效的测试用例至关重要。首先,全面覆盖测试是首要目标。这要求我们考虑所有可能的读写操作组合,包括从单字节读写到多字节读写,以及跨区间的读写操作。其次,边界情况的测试同样不可或缺。例如,DDR内存的满溢和下溢情况,即数据写入超出内存容量或读取不存在的数据时,系统对此的反应必须经过验证。若忽视对这些特殊情况的测试,一旦实际应用中出现类似情况,系统可能会崩溃或陷入异常状态。

正确的测试用例才能真正检验出DDR验证设计的有效性。

工具选择与使用

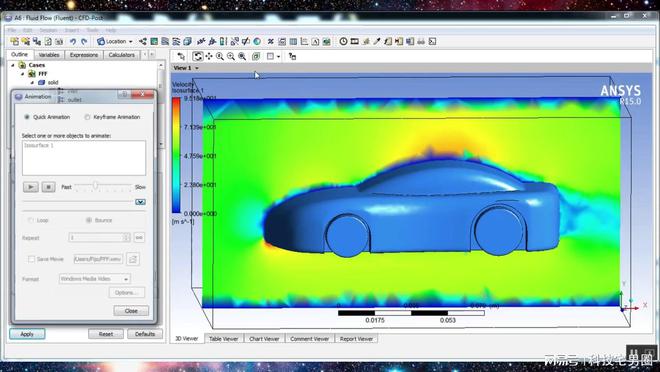

DDR验证设计中,合适的验证工具至关重要。一款优质的仿真工具能精确地还原DDR的实际工作环境。各类工具在功能上各有千秋,有的在时序分析上表现卓越,但在信号完整性检查上可能略显不足。挑选工具时,需结合项目实际需求。此外,熟练运用工具同样关键。一些复杂的工具需深入研习才能充分利用其全部功能,比如功能强大的示波器,若不懂得设置各项参数,便无法有效地进行信号检测。

如果工具运用不当,会给DDR验证带来许多不必要的麻烦。

故障排查

DDR验证时,故障检测是个难题。故障原因众多。首先,硬件问题很常见,比如芯片损坏或电路连接出了问题。有时,PCB板焊点松动会引起数据传输错误,这是经验之谈。其次,软件配置失误也不容忽视,比如DDR内存初始化参数设置错误。读写时序参数若与实际硬件不匹配,错误结果不可避免。

在DDR验证时,有一套科学高效的故障排查方法是非常必要的。

优化与改进

DDR验证设计一旦完成,便需进行优化与提升。首先,在确保数据准确传输的基础上,可尝试加快传输速率。比如,通过调整时序参数或优化布线,以降低信号传输的延迟。其次,在资源利用方面,应尽量避免不必要的电路消耗。比如,减少读写电路中的冗余设计。在具体项目实施中,追求性能与资源利用之间的平衡,才是我们追求的最终目标。

DDR技术在不断发展,验证设计也要与时俱进。

各位读者,我想请教一下,在DDR验证设计的过程中,你们觉得哪一部分最让人头疼?希望各位能点赞、转发这篇文章,并踊跃发表评论。