FPGA,即现场可编程门阵列,对DDR,也就是双倍数据速率的验证,在电子系统设计中扮演着至关重要的角色。DDR以其高速和大容量的特性,在现代电子设备中得到了广泛的应用。而FPGA对DDR的验证,正是保障系统稳定和可靠运行的关键环节。

理解DDR原理

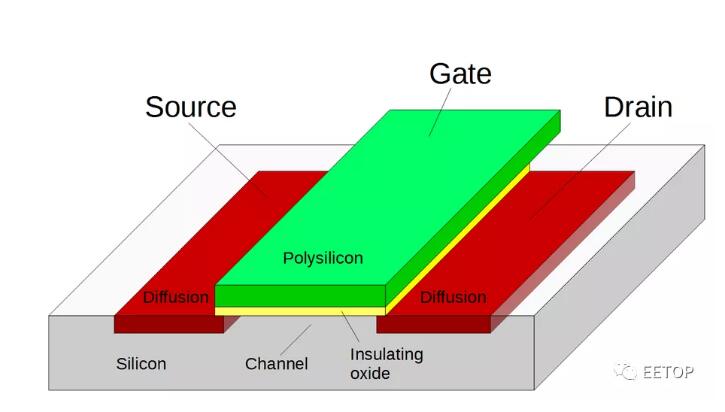

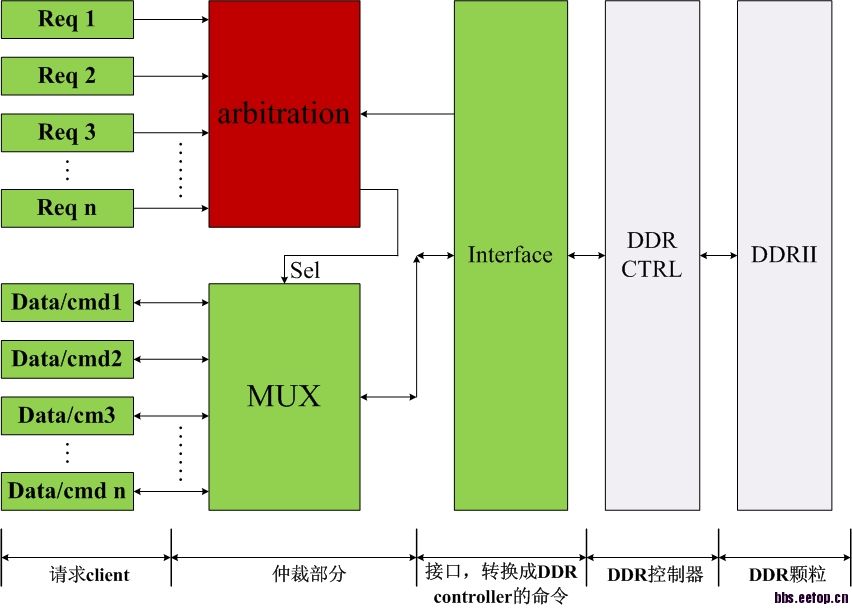

FPGA验证DDR,首先需对DDR的原理有深刻理解。DDR内存能在时钟周期的上升沿和下降沿进行数据传输,这显著提升了其数据传输速度,远超传统内存。然而,在电路设计中,DDR的工作机制相当复杂,包括预充电、刷新等操作。以显卡设计为例,要准确存储纹理数据并快速调用,必须对DDR原理有全面把握。若对这些原理缺乏理解,FPGA对DDR的验证工作将难以进行。从事相关工作的人员,必须仔细研读DDR原理手册,这是进行验证工作的基础步骤。

我们需要认识到DDR各版本间的区别,比如从DDR3到DDR4,它们在运作电压和数据传输速度等方面各有特点。这些差异对FPGA的接口设计及控制逻辑提出了新的挑战。

选择合适的验证工具

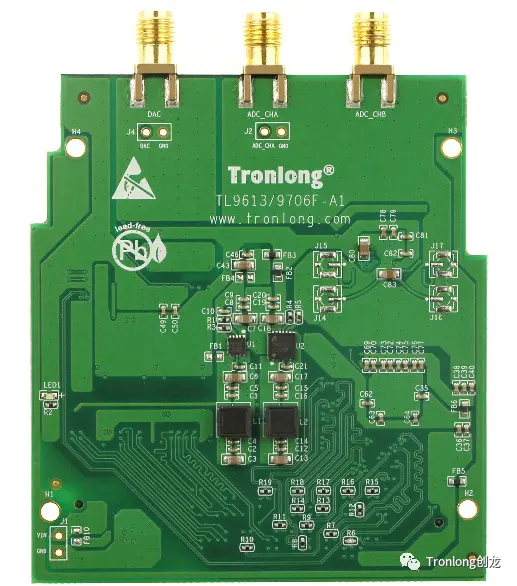

在FPGA验证DDR的过程中,合适的验证工具至关重要。这其中包括硬件工具,例如示波器等。示波器能让我们观察DDR的信号波形,便于及早发现信号完整性等问题。在高速数据采集系统中,示波器能捕捉到DDR数据传输的瞬间异常波形,帮助我们发现布线上的潜在问题。此外,还有软件工具,如专门的仿真软件。这些软件能模拟DDR在不同工况下的工作状态。许多仿真软件拥有丰富的DDR模型库,便于快速验证设计,提升验证的效率和准确性。

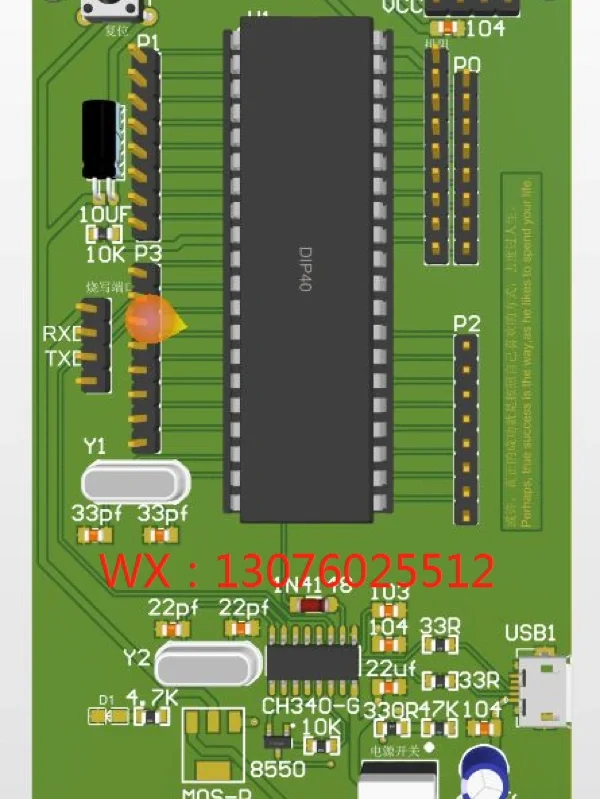

不同的FPGA开发板在使用验证工具时存在差异,这要求我们依据具体的硬件条件来挑选合适的工具,并相应地调整使用策略。

创建验证环境

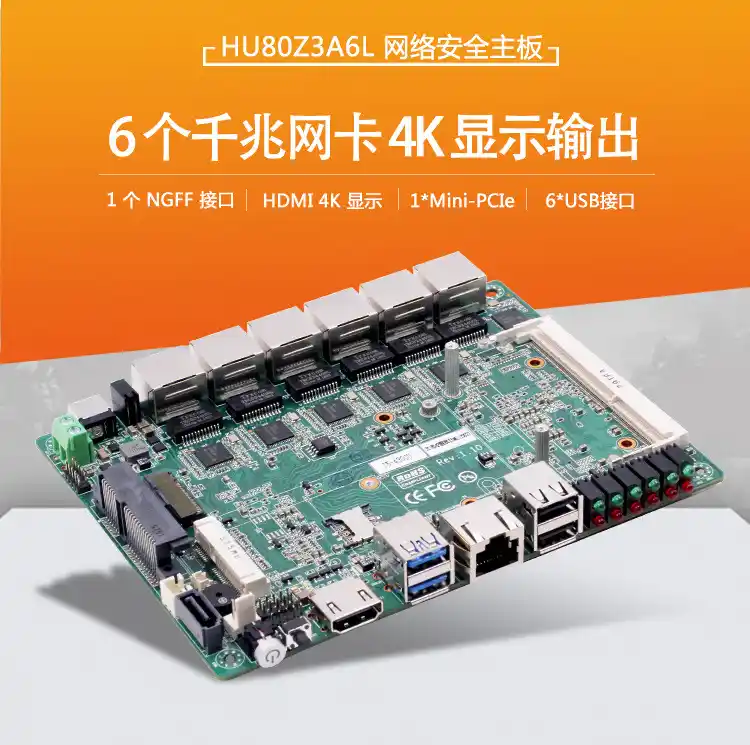

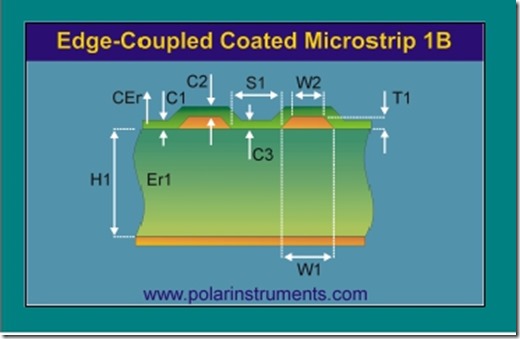

构建一个适合的验证环境至关重要。首先,需要明确FPGA与DDR之间的连接拓扑,比如选择是星型还是菊花链。星型拓扑有助于提升系统稳定性,但布线可能相对复杂。在大规模数据存储系统中,恰当的拓扑结构能有效避免数据传输中的干扰。同时,还需注意电气特性的匹配,比如信号的驱动能力。若驱动能力不够,DDR信号的上升沿或下降沿斜率可能不足,进而影响数据读写准确性。

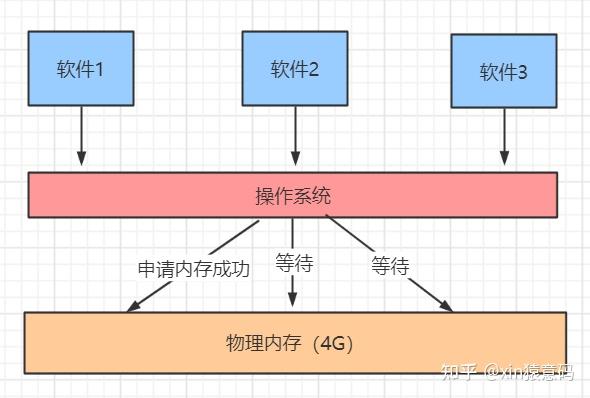

电源管理同样需要在验证环境中得到考虑,DDR对电源的稳定性要求相当高。电源不稳定,数据错误便难以避免。

编写测试用例

在FPGA验证DDR的过程中,编写测试用例至关重要。首先,必须关注常规的读写操作测试用例。这包括对DDR从单个字节到多个数据块的读写测试,以确保在不同地址下数据的准确性。比如,在通信基站中,要测试从空闲状态到满负荷状态切换时DDR的数据读写情况。此外,还需考虑异常测试用例,比如电源波动时DDR的行为,以及数据线或地址线干扰下的DDR工作状态等。编写全面的异常测试用例,有助于提高系统的抗干扰能力。

这些测试用例并非一蹴而就,编写过程中常常需要根据验证时遇到的问题进行持续的调整与完善。

进行验证调试

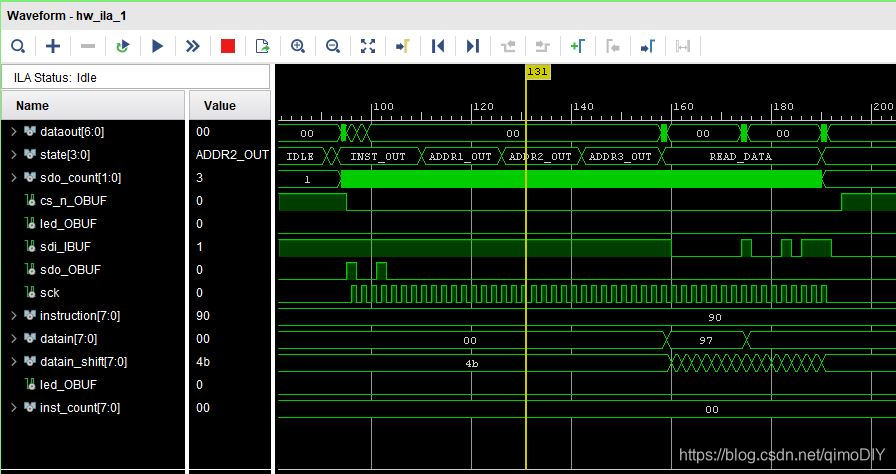

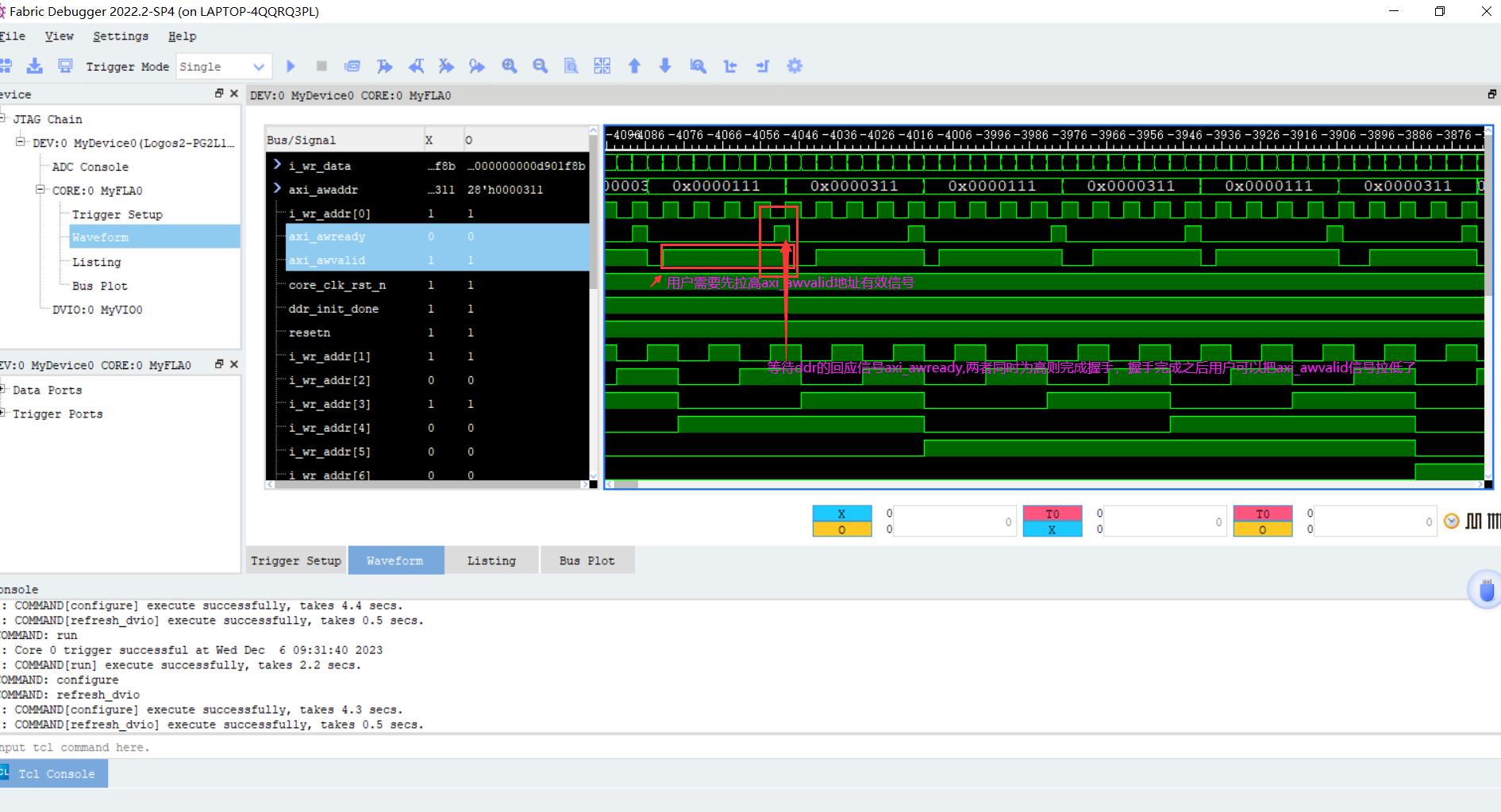

进入验证调试阶段,这个过程既复杂又费时。首先,要进行时序调试,确保FPGA与DDR之间的所有信号都符合时序要求。比如,数据的建立时间和保持时间必须达标,否则会产生亚稳态,导致数据错误。为此,需要不断调整FPGA内部的逻辑时延。其次,是功能性调试,要检查读写功能是否完全正常,以及ECC纠错等高级功能是否能有效运作。在复杂的服务器系统中,ECC纠错功能的正确实现对于数据安全至关重要。

调试过程中,要熟练运用先前提到的验证工具。同时,应详尽记录调试时产生的数据和波形。这样做,是为了便于后续的深入分析。

结果分析与优化

完成验证和调试后,便进入结果分析阶段。需仔细核对验证结果中的各项数据,若发现数据有误,务必深入探究其成因。原因可能在于硬件布局布线问题,亦或是测试用例存在缺陷。接下来,开展优化工作,对硬件设计进行修改或完善测试用例。结果分析与优化是一个持续反复的过程,直至FPGA对DDR的验证完全满足要求。

在FPGA验证DDR的过程中,你是否也遇到了让人头疼的问题?不妨来评论区交流互动。若觉得这篇文章对你有所帮助,不妨点赞并分享给更多人。