DDR内存条在众多电子设备中扮演着关键角色,而quartus作为一款关键的开发工具,与之相关的DDR读写操作涉及众多技术细节,这些都需要我们深入学习。这些知识对于提升开发板的性能和实现其功能至关重要。

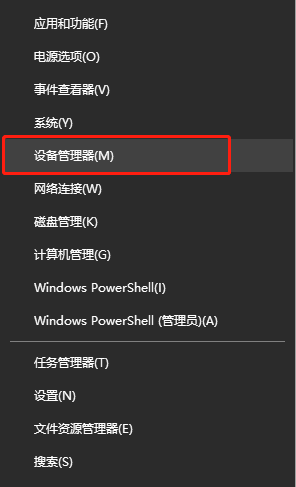

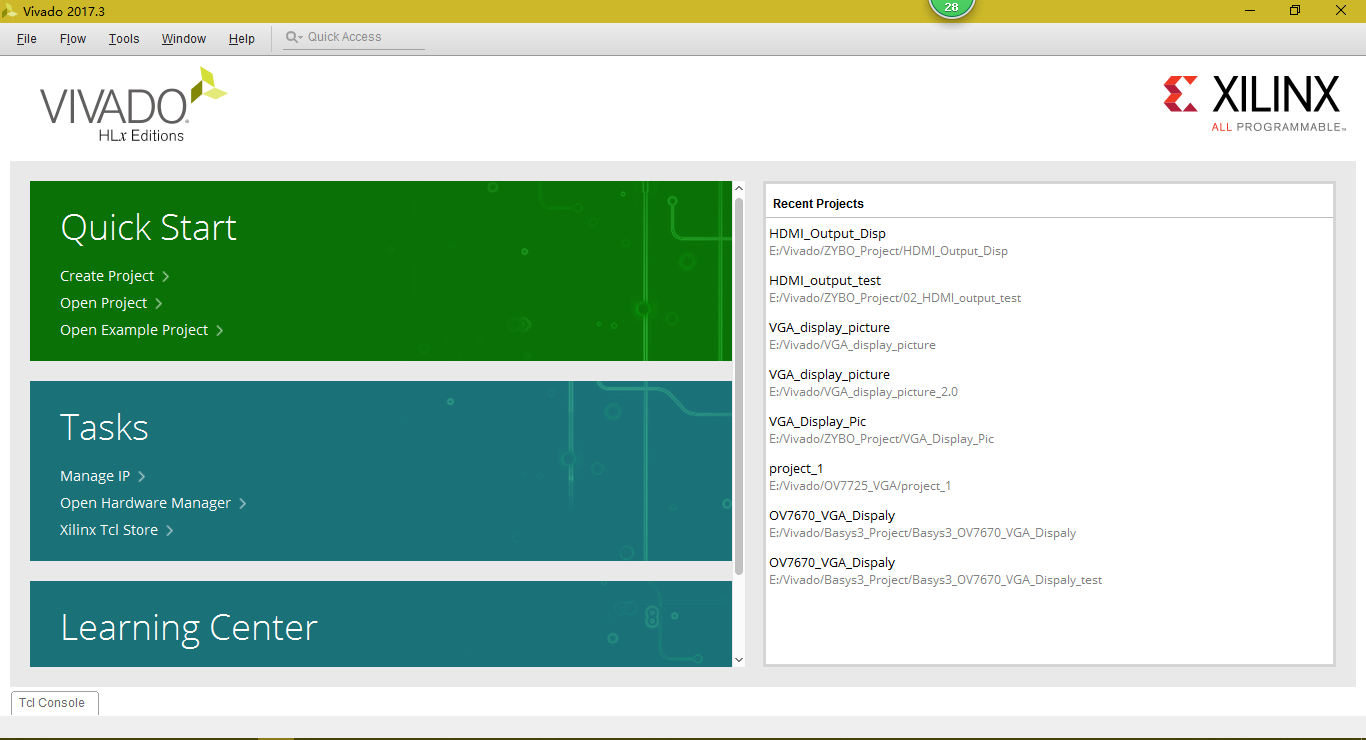

Quartus环境搭建

进行DDR读写操作前,首先必须搭建好恰当的开发环境。务必要确认quartus软件的适宜版本已正确安装。安装过程中可能会遭遇失败或版本兼容等难题,例如,新版本可能与现有硬件不兼容。此外,还需依据所使用的开发板型号,安装相应的BSP包,这一环节同样可能遇到驱动与硬件不匹配的问题。因此,我们不仅要仔细阅读硬件设备手册,还需多次进行安装和测试。

环境搭建正确是前提,这样才能为DDR的读写操作奠定基础。若这个基础不稳固,后续的工作便会遇到困难。许多新手往往忽略了这一点,急于求成,忽略了环境搭建的重要性。

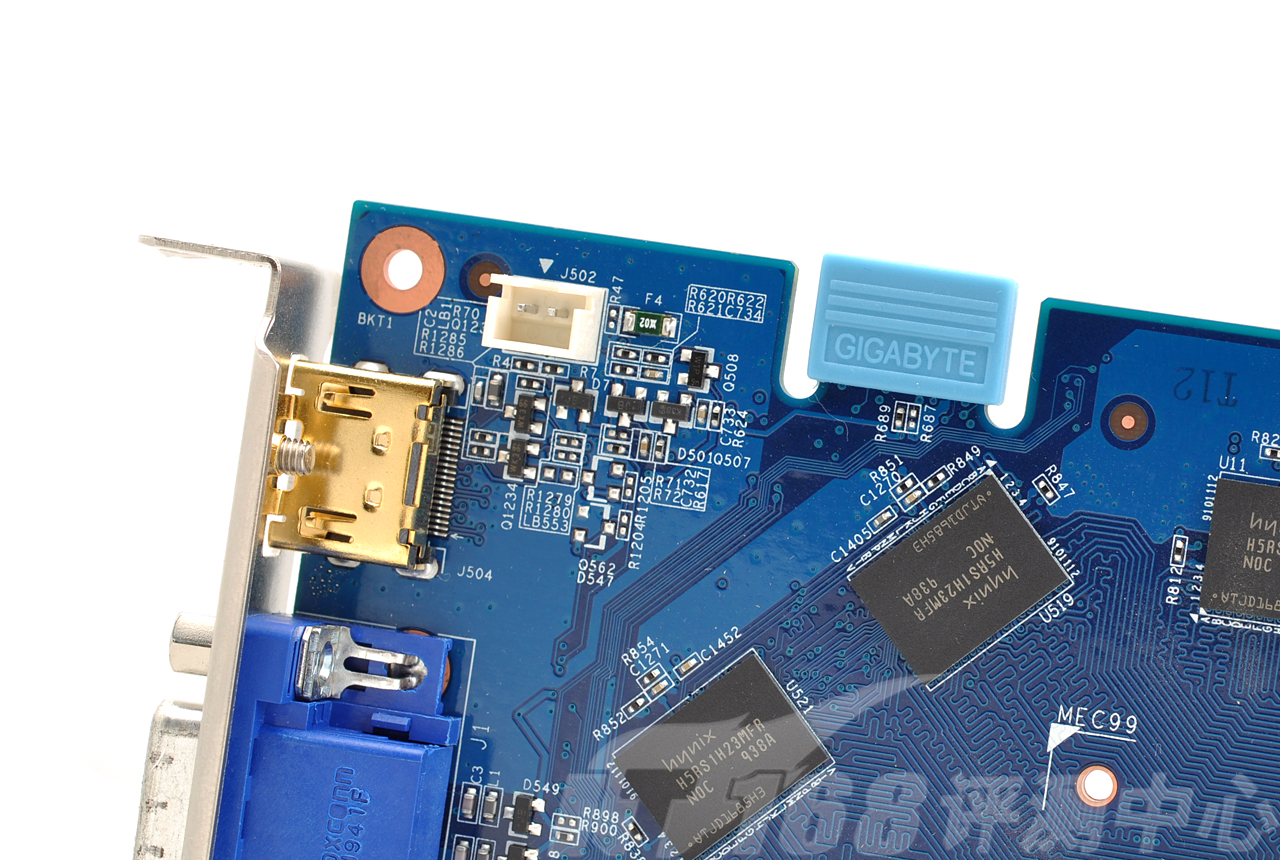

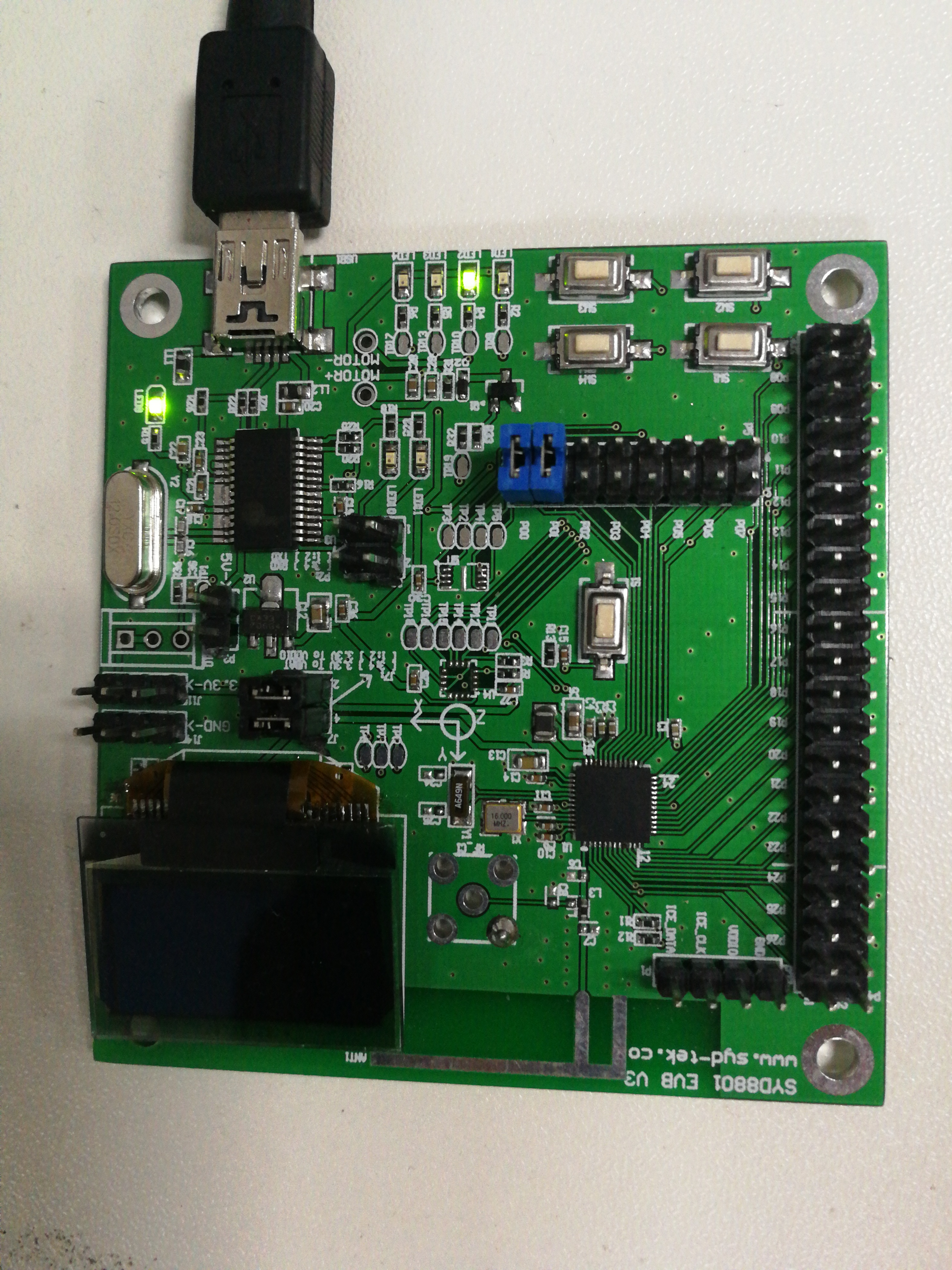

DDR硬件连接理解

DDR的硬件连接至关重要,它直接关系到读写操作的准确性。无论是物理线路还是芯片管脚的连接,都必须清晰明确。例如,数据信号线、地址信号线和时钟信号线的连接方式至关重要,错误的连接可能会导致数据传输出错。此外,还需关注DDR的Bank数量和位宽等硬件参数,因为这些参数将直接影响我们在quartus中进行读写操作时的配置。

此外,硬件连接的品质同样对信号是否稳定起着关键作用。线路若过长,或是信号线遭受干扰,便可能引发数据读写时出现乱码或是错误。因此,在设计硬件之初,我们必须确保布线合理,并采取有效的屏蔽防护措施,绝不可掉以轻心。

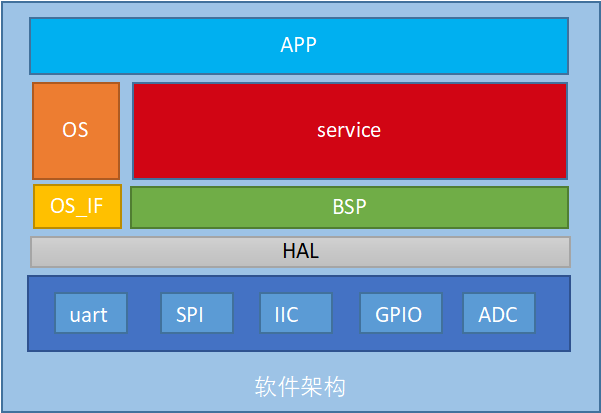

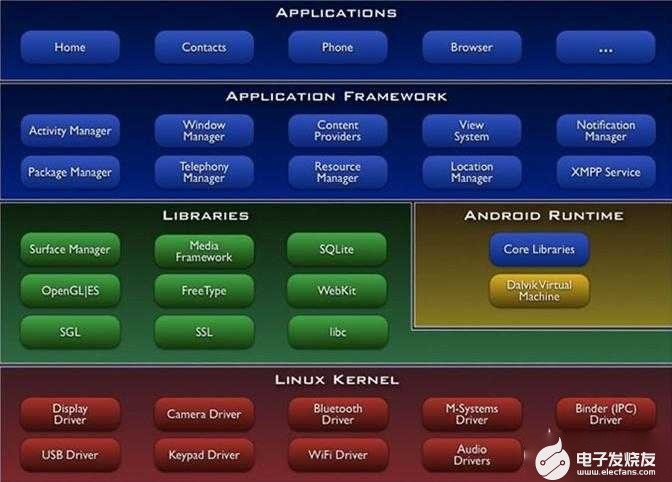

IP核的配置

IP核在quartus软件中对于DDR的读写操作至关重要。首先,我们必须学会根据DDR的具体类型和硬件参数来准确挑选IP核。若选错了IP核,读写操作可能会无效,甚至性能会大幅下降。在配置IP核的过程中,数据位宽、频率等参数必须细致设置。例如,若数据位宽设定不当,数据传输便会出现错误。

IP核的初始化顺序和参数校验同样至关重要。若初始化顺序有误,IP核可能无法正常运作。因此,我们必须反复检查IP核的配置是否准确无误,这一步骤对于确保DDR读写操作能够顺利进行是必不可少的。绝不能仅依赖默认参数草率行事。

DDR读操作

DDR的读操作,关键在于准确获取地址。首先,我们需要发送读请求信号;接着,按照规定的顺序来获取数据。这个过程对时序要求极为严格。一旦时序出错,读取的数据可能会出现乱序或错误。以多Bank的DDR为例,对Bank的选择时机和地址转换顺序都有明确的要求。

操作读取数据时,必须留意数据缓存的相关问题。缓存配置若不当,数据可能会丢失,亦或是读取速度变得缓慢。因此,我们必须依据实际需求,对缓存的大小和读取策略做出恰当的调整。

写操作与读操作虽有许多相似之处,却也存在差异。首先,写地址的设定必须精确无误。我们需在恰当的时钟周期内,将数据及其对应写地址传递至DDR。同读操作一般,写操作亦遵循严苛的时序规范。若时序出现混乱,写入的数据可能出错或丢失。

写操作还需注意数据宽度的适配。写入DDR之前,数据可能需先处理,以保证其宽度与DDR规格相符。同时,在满载状态下的写操作处理同样重要,不能无节制地写入,而忽视DDR的容量状况。

读写性能优化

完成基础的读写操作后,我们通常还需对性能进行提升。首先,可以从提升数据传输的频率着手,这样做能在一定程度上提升读写速度。然而,在提高频率的同时,我们还需关注信号的稳定性,避免因过度追求速度而引发数据错误。

另外,调整读写指令的顺序也能起到一定作用。合理地编排指令,能提升DDR的效率。例如,可以将读取同一区域的数据请求汇集,使DDR能连续执行读操作。我想请教大家,在使用quartus进行DDR读写优化时,有没有遇到过什么特别棘手的问题?如果觉得这篇文章对您有帮助,请点赞并分享。