Xilinx的DDR(双倍数据速率)效率,在技术领域占据着重要地位。简言之,DDR效率直接影响数据的传输速度、存储,以及系统的整体性能。它是评估系统能否高效稳定运行的关键指标之一。

了解DDR基本原理

DDR在数据传输中遵循特定的设计规则和原理。首先,它通过实现比普通SDRAM快一倍的数据传输速度,从而提升了读写效率。这一点是其运作机制的核心,也是它被广泛使用的原因之一。比如,在网络设备这类需要高速数据处理的场合,DDR的高速传输特性能够确保数据的快速流动。此外,DDR的同步工作模式也是其原理的关键部分。这种同步操作使得数据读写等操作更加精确和高效。了解这些原理对于我们深入研究如何提升DDR效率大有裨益。

为了提升DDR的效率,我们得深入掌握其运作原理。DDR的效率并非由单一因素所决定,这一点在众多复杂的电子系统设计中尤为明显。若忽视了DDR的基本原理,就很容易导致其效率降低。

硬件设计的影响

硬件设计对DDR效率的提升至关重要。良好的布线设计能降低信号干扰,从而提高DDR的效率。DDR信号速度较快,若布线不当,易引发串扰等问题。比如在PCB板布局阶段,合理规划DDR布线的宽度和间距十分关键。此外,电源质量的好坏也对DDR效率有影响。电源不稳定会使DDR工作不稳定,甚至引发数据错误。

在实际生产中,我们常遇到这样的情况:若在硬件设计的初期阶段忽略了DDR效率相关的硬件因素,那么即便后续投入大量资源,也难以完全弥补DDR效率的损失。此外,一旦硬件设计确定下来,修改所需的成本通常也会非常高。

软件环境设定

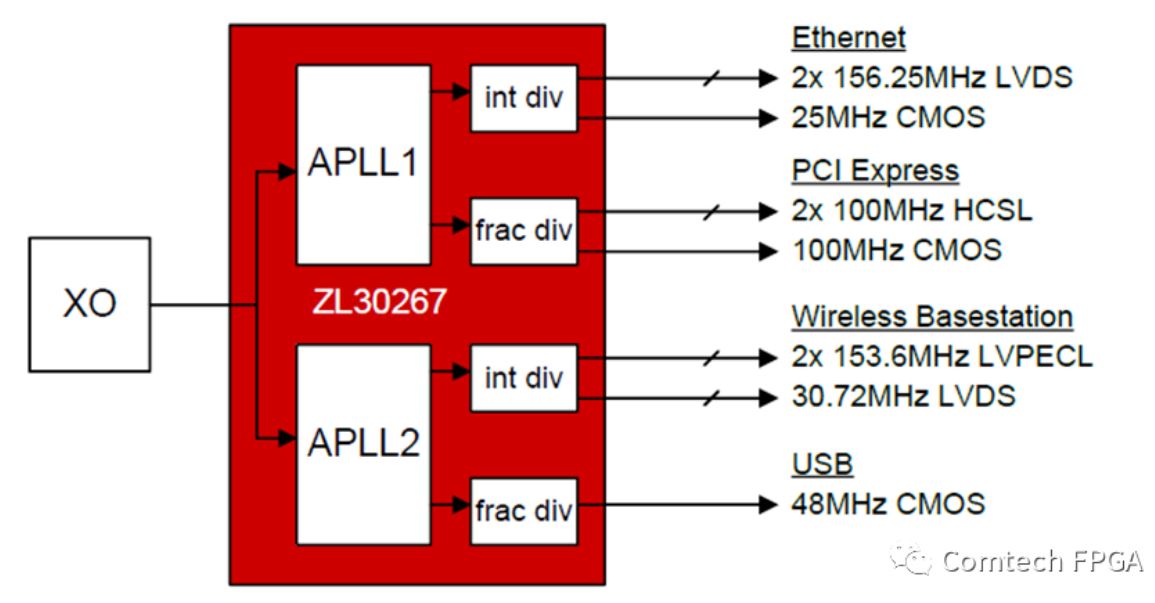

软件环境的配置对于提升XilinxDDR的效率至关重要。驱动程序的配置是这一过程中的基石。若驱动程序不匹配或存在缺陷,DDR的性能将无法达到最佳。在众多使用Xilinx芯片开发的项目中,开发者常常需要抉择使用哪个版本的驱动程序更为适宜。此外,内存控制器的参数设定同样关键。恰当的参数设置能让DDR根据实际需求高效运作。

在软件的实际操作中,我们常会发现,一个微小的软件设置调整,就能显著提升DDR的效率。然而,由于开发者们往往忽略了这一点,他们常常花费大量时间寻找所谓的硬件问题。

优化数据读写模式

数据的读写模式是DDR效率的关键因素。合理的读写顺序能有效缩短读写时间。比如,在处理数据密集型任务时,遵循一种有逻辑的读写顺序,就能避免不必要的寻址时间浪费。此外,采用合适的缓存策略也能提升DDR效率。恰当的缓存策略能减少对DDR的直接访问次数。

在具体应用场景中,若对数据的使用模式进行深入研究,便能调整读写模式,从而提升DDR的效率。然而,很多时候,要么是因为缺乏相关知识,要么是因为没有进行深入分析,DDR的效率并未得到充分利用。

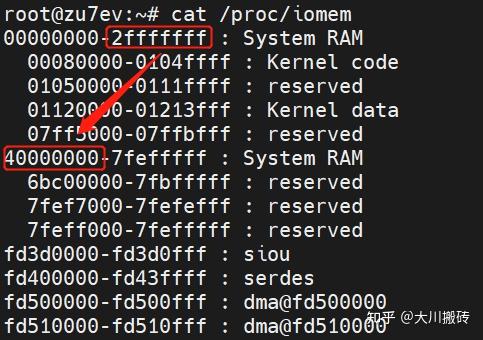

测试与调试

提升DDR性能的关键在于测试与调试。性能测试能让我们直接看到DDR的当前效率。借助专门的测试工具,我们能精确获取DDR在特定条件下的读写速度等关键数据。调试工作则是对测试中暴露出的问题进行针对性处理。比如,若发现DDR效率不高,我们便需通过调整硬件电路或软件参数来优化其性能。

在具体的项目实践中,不少团队没有充分认识到持续测试和调试的重要性。他们在开发初期仅进行了有限的测试,这样的做法使得DDR效率的全面优化变得困难,同时,对于DDR效率可能出现的下降问题,也难以做到及时发现和处理。

持续监测与改进

DDR效率的监测和优化需持续进行。系统运行时间延长或业务需求变动时,DDR效率可能波动。因此,定期观察DDR的工作状态至关重要,以便及早发现效率的变动。若发现效率降低,应立即实施改进措施。这些改进可能涉及硬件的优化或软件的调整。

在实际操作中,我们常常只关注项目初期的安装,却忽视了系统长期运行中的维护。在Xilinx的DDR效率管理上,您是否有过独到的经验或看法?欢迎点赞、转发和留言讨论。