在这篇文章中,我要向大家介绍DDR引脚DQS的相关知识。DQS是DDR内存中一个至关重要的概念。它在数据传输过程中扮演着核心角色。对深入理解DDR内存的工作机制和性能优化具有极其重要的价值。

DQS的基本概念

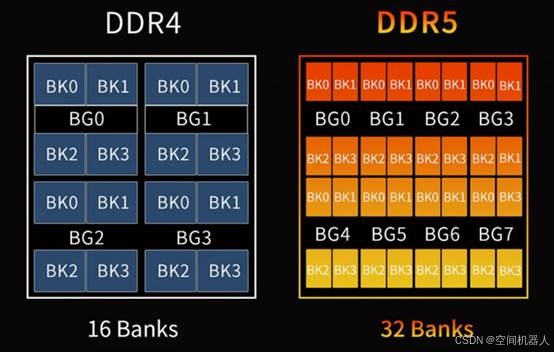

DQS,全名是DataStrobeSignal,即数据选通信号。在电路设计领域,这个引脚的主要作用是满足DDR同步工作的需求。DDR内存运行时,数据是双向传输的,而DQS则是确保数据准确读写的关键。它需要与时钟信号协同配合,一旦DQS出现问题,数据传输的稳定性就会大大降低。此外,DQS信号在上升沿和下降沿都能触发数据的读取或写入,这一点与其他信号有所不同。

内存的正常运作依赖于DQS信号的精确度和准确度。若DQS的频率或相位出现误差,数据错误的风险便会增加。以读取数据为例,若DQS信号的时序不够准确,那么读取到的数据可能就是错误的,甚至是不完整的。

DQS在数据传输中的角色

DQS在数据传输中扮演着指挥家的角色。DDR内存的一个显著特点就是数据的并发传输。在这一过程中,DQS掌控着数据传输的节奏。通常,每个DQS周期都会对应数据线上多个比特数据的传输。若将数据比喻为一队正在行进的士兵,那么DQS就像是这支队伍的指挥官。举例来说,当DQS处于上升沿或下降沿时,数据线上相应的有效数据就会被保存或读取。

在高速数据传输的环境中,DQS能保证数据的有序和准确无误。若没有DQS信号进行良好的同步控制,由于传输速度极快,数据丢失或错序的情况极有可能发生。此外,在多组数据传输过程中,DQS还能有效管理各组数据间的交互和顺序。

DQS与时钟信号的关系

DQS与时钟信号关系密切。它们宛如一对默契的舞伴,共同协作。时钟信号负责提供基础的时钟节拍,而DQS则需要按照时钟信号的节奏来发出数据选通信号。时钟信号按照固定频率发出脉冲,DQS则在这个节拍的基础上决定何时启动数据选通。

时钟信号一旦出现异常抖动,便可能引起DQS相对位置的混乱。即便现代电路设计拥有补偿机制,细微的时钟偏差仍可能干扰DQS信号的有效性。此外,DQS信号也会对时钟信号产生反作用。若DQS信号负载过重或发生串扰,时钟信号的稳定性和准确性同样会受到干扰。

DQS信号的检测与调试

检测DQS信号是确保DDR内存稳定运行的关键措施。在硬件设计和调试过程中,我们常借助示波器等工具来观察DQS信号的波形、频率以及相位。若发现波形呈现不规则形态,比如出现毛刺或变形,这往往预示着DQS信号可能存在异常。

调试时若遇数据传输故障,不妨先检查DQS信号是否运作正常。调整DQS信号的相位,往往能解决因时序问题引起的数据传输错误。然而,在生产环境中进行此类调试较为复杂,因为可能涉及多种影响因素,需全面考虑并进行分析。

DQS对性能的影响

DQS对DDR内存性能的影响十分明显。一个稳定且精确的DQS信号对于提升DDR带宽大有裨益。若DQS信号能精确调控数据传输的时间点,数据传输的效率便能显著提高。

若DQS信号存在故障,不仅会引起数据传输失误,而且会限制内存的工作频率。换言之,原本能以高频运行的DDR内存,因DQS信号的问题,不得不降低频率以确保数据传输的稳定性。比如,在那些对内存性能要求极高的游戏或数据处理场景中,一旦DQS信号不稳定,其性能将显著下降。

DQS的未来发展

技术不断进步,DQS也遭遇了不少改进的机遇和挑战。首先,DDR内存性能的持续增强,使得对DQS信号的精确度和稳定性提出了更高的要求。其次,为了确保DQS信号的有效性,未来的电路设计中可能会引入更多的补偿与校正机制。

新兴的内存技术或许会对DQS这一概念带来变革。未来,可能会有全新的信号传输与控制技术取而代之。然而,不管怎样,目前对于DQS的研究与优化,依然是DDR内存技术发展不可或缺的一环。

在使用DDR相关设备时,你是否遇到过数据传输问题?这可能与DQS信号有关。欢迎大家在评论区留言讨论,同时,也希望大家能点赞并分享这篇文章。