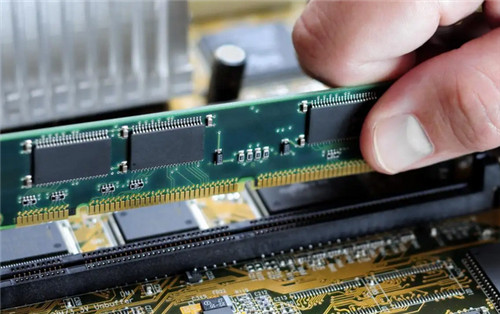

在现代电子系统中,PL(可编程逻辑)和DDR(双倍数据速率)技术的结合显得尤为重要。DDR技术能够实现高速的数据传输,满足系统对内存性能的高要求。而PL技术则能进行灵活的编程,控制逻辑功能。当这两种技术结合使用时,它们之间存在着巧妙的技术联系。

PL与DDR的应用场景

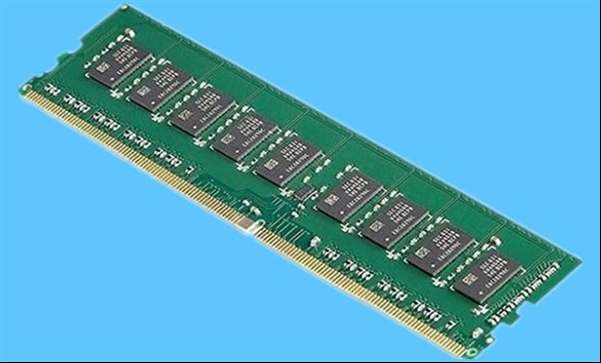

在现代科技设备中,DDR技术被广泛用于数据存储。以高端计算机为例,其内存便是DDR技术的典型应用。这些设备对内存数据传输速度的要求较高。可编程逻辑控制器(PLC)能根据不同应用需求,灵活编写DDR相关逻辑。在特定工业控制设备中,PLC同样需要适配DDR以实现数据的快速处理。这样做可以优化设备性能,提升工作效率。实际上,设备类型的多样性决定了PLC编写DDR逻辑的复杂程度。比如,小型嵌入式设备可能只需简单的逻辑控制,而大型服务器则需更为复杂的逻辑处理。

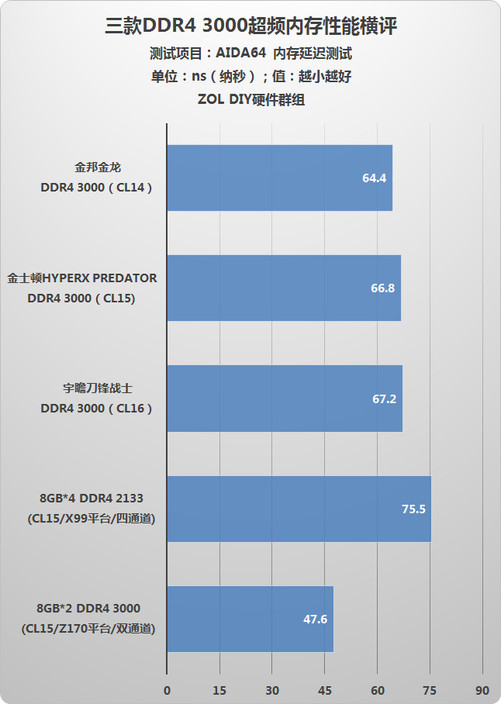

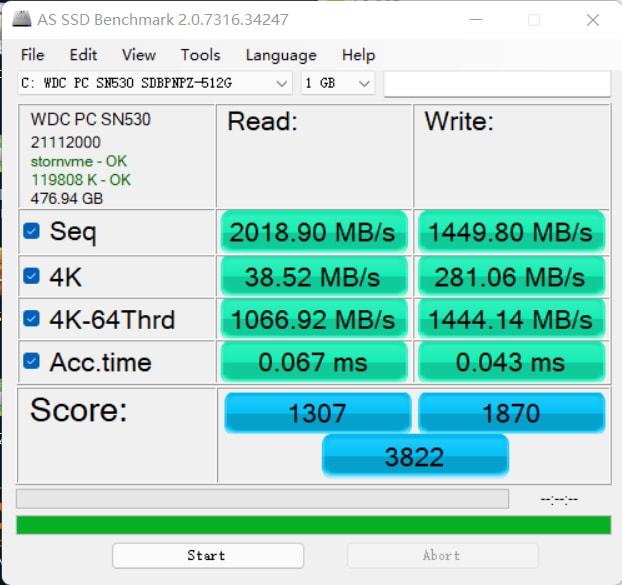

从开发者的视角出发,他们必须透彻掌握各类DDR协议的精髓。以DDR3和DDR4为例,它们各自有着独特的协议特性。若要在PL中编写针对DDR4的DDR逻辑,就必须严格遵循其协议规范进行操作。这一点在实际应用中至关重要。不同的协议决定了数据传输的途径和速度等关键信息,若不熟悉协议,便无法完成正确的PL写DDR。

PL的选择对DDR性能的影响

PL芯片在处理能力和功能上存在显著差异。高端PL芯片能执行更复杂的逻辑控制,写入DDR内存。相比之下,低端PL芯片在处理复杂逻辑和高速DDR控制方面可能力不从心。若项目预算充足,宜选用高端PL芯片以实现DDR性能的最大化。若预算有限,选用低端芯片可能导致DDR数据传输速度不达预期,甚至在高负荷数据处理时出现错误。

从技术兼容性角度分析,部分PL芯片与多种DDR版本表现出良好的兼容性,而另一些则仅限于与特定DDR版本相匹配。以某款常见的PL芯片为例,它对DDR3和DDR4的支持表现良好,但对于即将问世的DDR5,可能存在兼容上的难题。这一情况对PL芯片在设计初期的选择与测试提出了更高要求,目的是避免产品上市后因兼容性问题而遭受损失。

PL写DDR的编程思路

编程的第一种思路是以模块为基础。具体来说,将PL和DDR的功能划分为若干模块,诸如数据读取模块、数据写入模块以及控制模块等。以图像采集处理系统为例,数据读取模块负责从DDR中提取图像数据,而写入模块则负责将处理过的图像数据存回DDR。这样的设计便于代码的维护与调试。

还有一种编程方式着眼于功能的实现。比如,可以依照数据处理的时间顺序来编写对DDR的操作代码。以音频处理设备为例,先读取音频数据,接着进行特效处理,最后将处理后的音频数据写回DDR存储,这样的逻辑顺序来编写程序。这种编程方式能高效地完成特定功能,但若要在之后添加新功能,修改起来可能会较为繁琐。

PL写DDR的挑战

时序问题首先显现。DDR数据传输对时序的精确度要求极高,一旦PL写入DDR时序控制不当,便可能引发数据传输错误或不稳定。这好比在精准的心跳节拍中跳舞,稍有失误便可能全盘皆输。在实际操作中,通常需要借助精确的时钟管理电路来保证PL写入DDR的时序准确无误。

资源利用确实是一项挑战。在PL内部,资源是有限的。在编写DDR时,既要高效利用资源,又要保证DDR的性能,这两者之间的平衡很难把握。特别是在像物联网设备这样资源受限的场景中,我们必须细致规划资源的分配与使用,以确保PL能够正常进行DDR的低功耗等操作。

PL写DDR的优化技巧

代码模块化,这是一种非常实用的优化手段。将PL编写DDR的代码进行模块化处理,便能轻松实现代码的复用。比如,在多个项目中,若DDR的操作流程有部分相似,便可以直接使用这些模块。此外,它还便于调试,一旦某个模块出现问题,我们能迅速找到并修正。

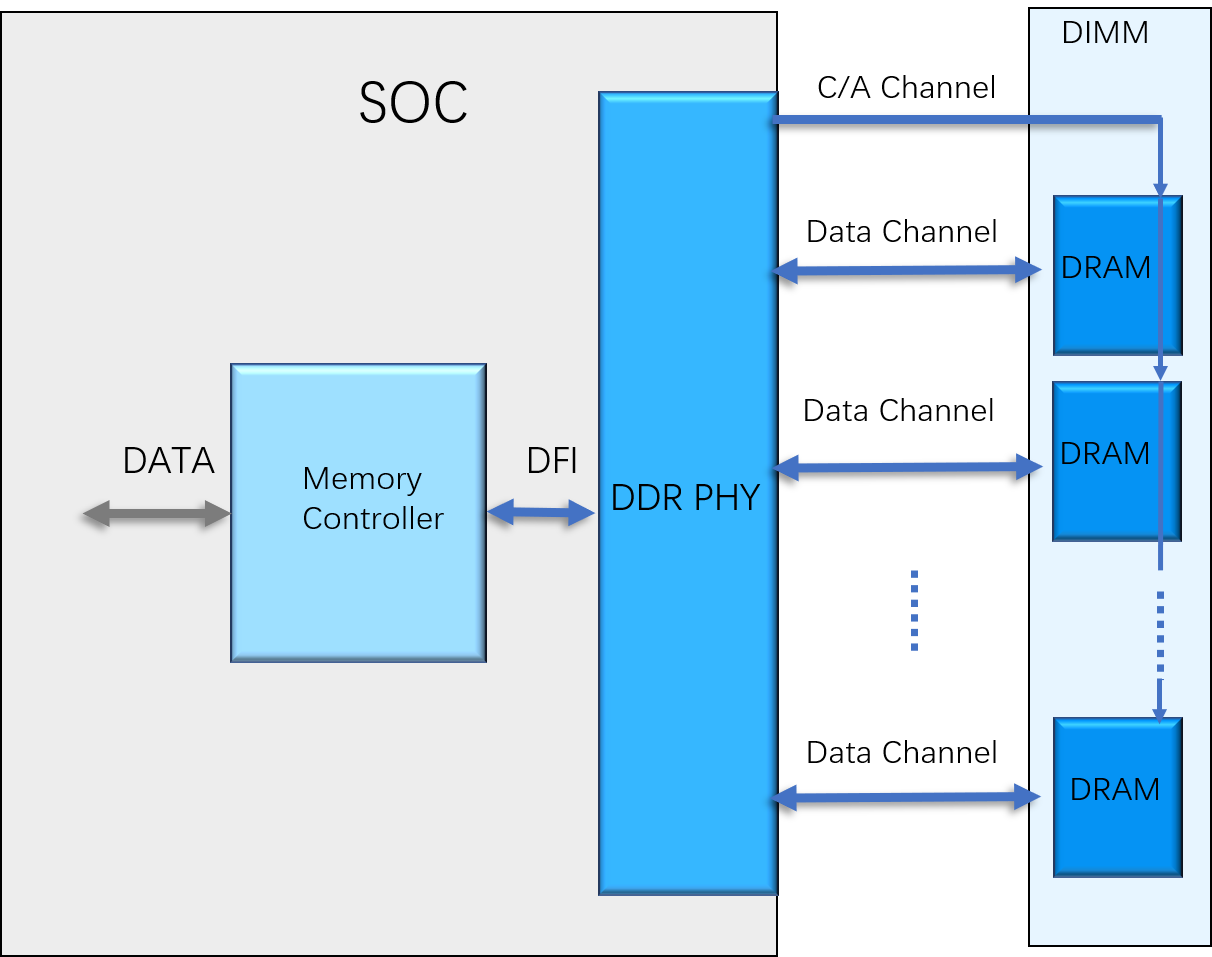

多通道应用,这是另一种技巧。通过设立多条数据通道,将数据传输至DDR,可以显著提升数据传输的整体效率。特别是在视频处理等需要大量数据传输的场合,若能巧妙运用多通道,便能大幅增强系统性能,有效缓解数据处理拥堵的问题。

PL写DDR的发展趋势

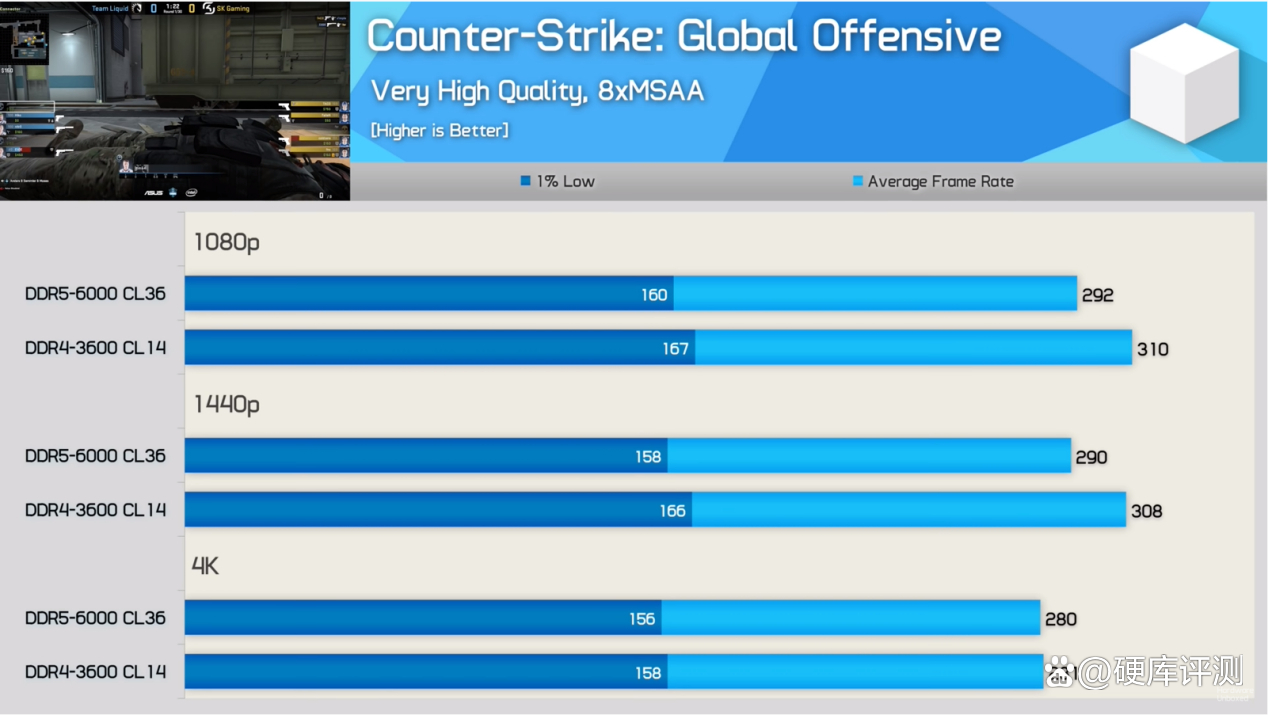

技术不断进步,PL编写DDR正朝着更快的速度迈进。比如,从DDR3升级到DDR4,再到未来的DDR5,数据传输速率持续提高。这一变化使得PL必须编写出能够适应更高传输速度的DDR逻辑。

随着智能化的发展,PL编写DDR的过程同样需要更智能、更自动化的控制逻辑。未来,当设备进行PL编写DDR操作时,应能根据系统负载和功能需求自动调整和优化。为此,我们在技术研发上需不断深入探索和创新。

大家对PL在今后创作DDR时可能会遇到的哪些新难题有什么看法?不妨积极留言交流。若觉得本文对您有所帮助,不妨点个赞,也欢迎转发分享。