身为资深系统工程师,于设计过程中,曾面临诸多挑战。在此篇文献中,我愿分享关于DDR内存地址寻址部分的心得体会。谨列出以下七大要点,望能为同行工程师提供参考。

1.熟悉DDR标准

首当其冲,身为DDR寻址规划的从业人员,需深知DDR相关规范。了解包括基础原理、数据传输过程及各项时序需求等方面的内容至关紧要;唯有深入掌握DDR规范,方能精确设计出稳固而有效的系统。

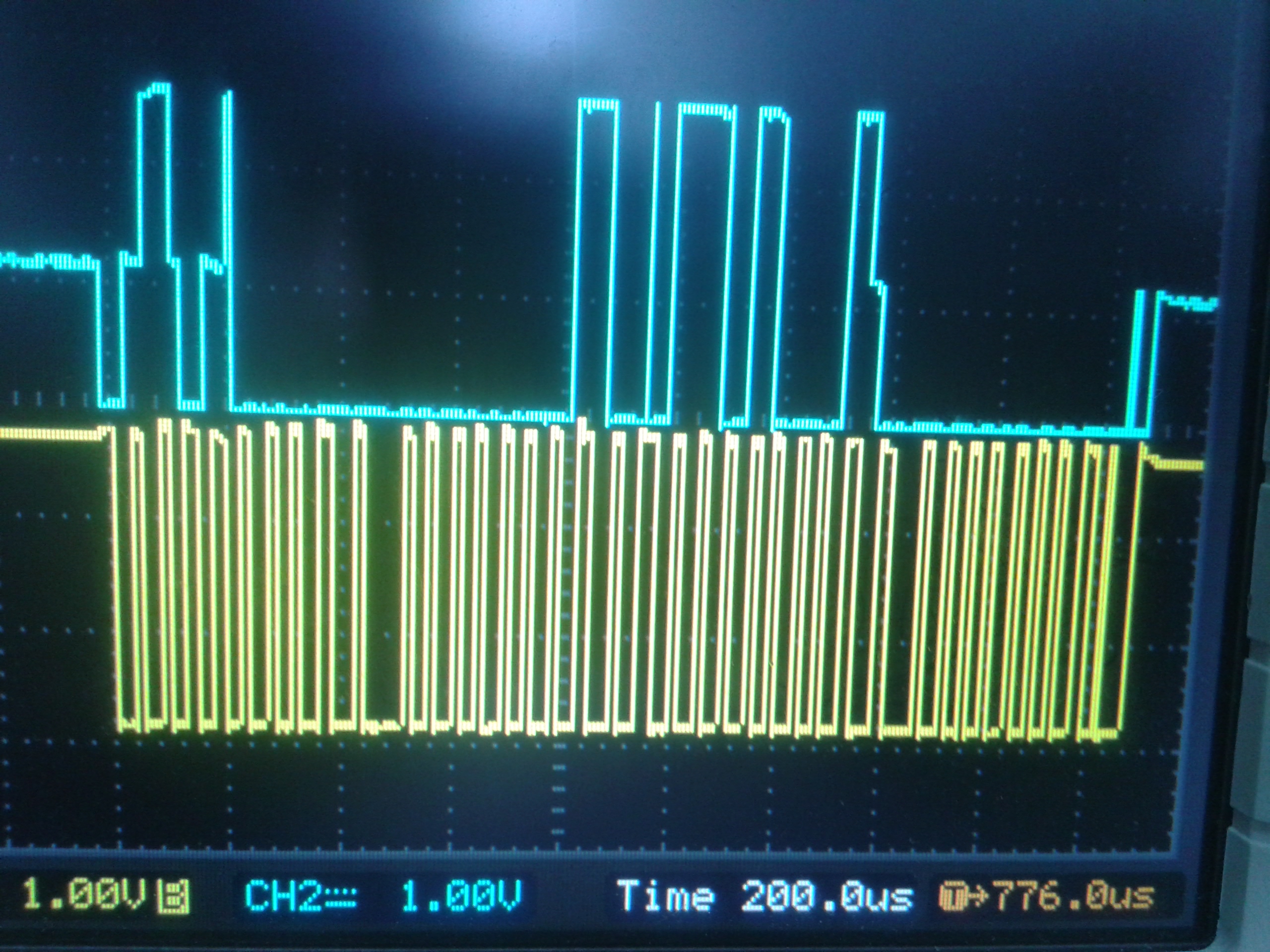

2.考虑信号完整性

DDR读取地址设定中,信号完整性的考量至关重要。必须控制其传输中的噪扰影响,如噪声、串扰,保障完美的信号波形质量,须采用合理线路布置,准确选取信号粗细度及阻抗匹配等策略。

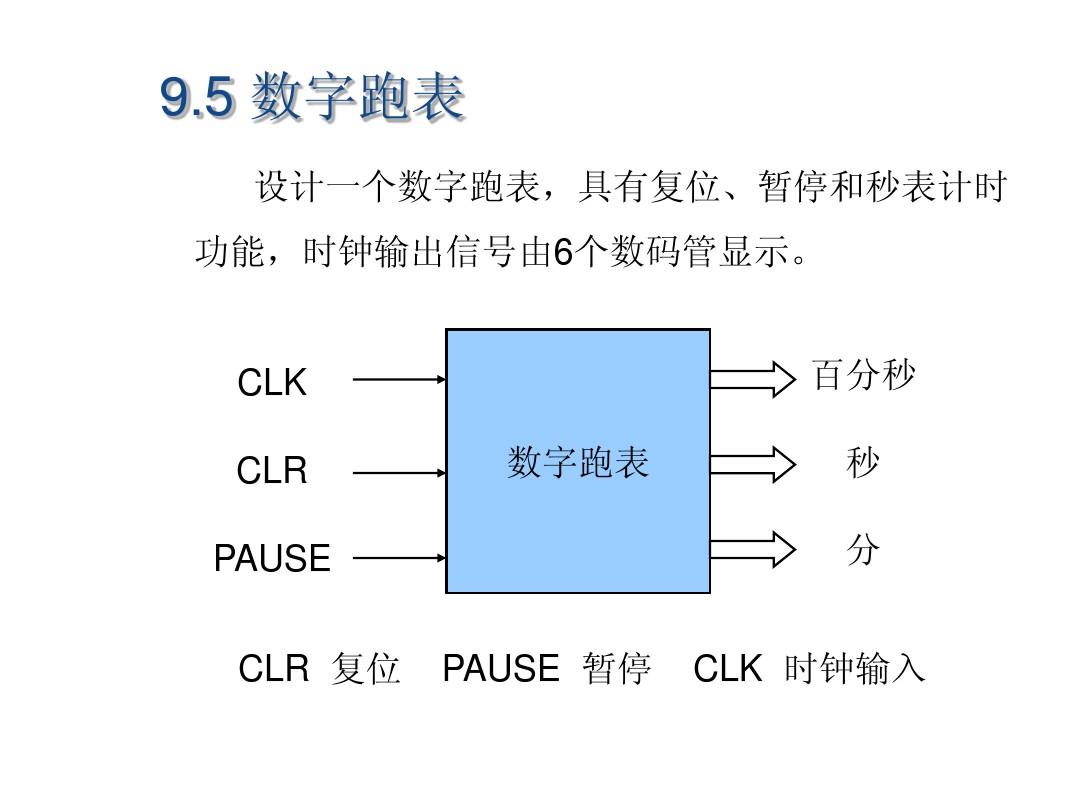

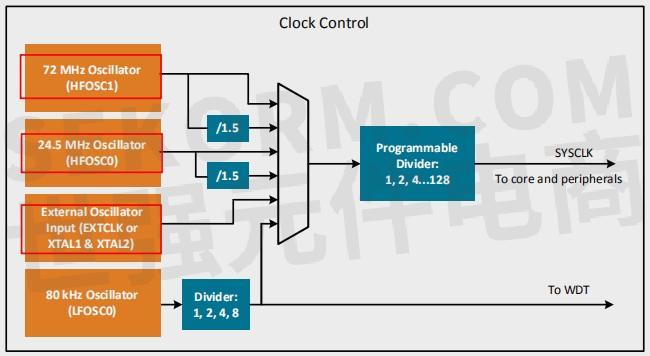

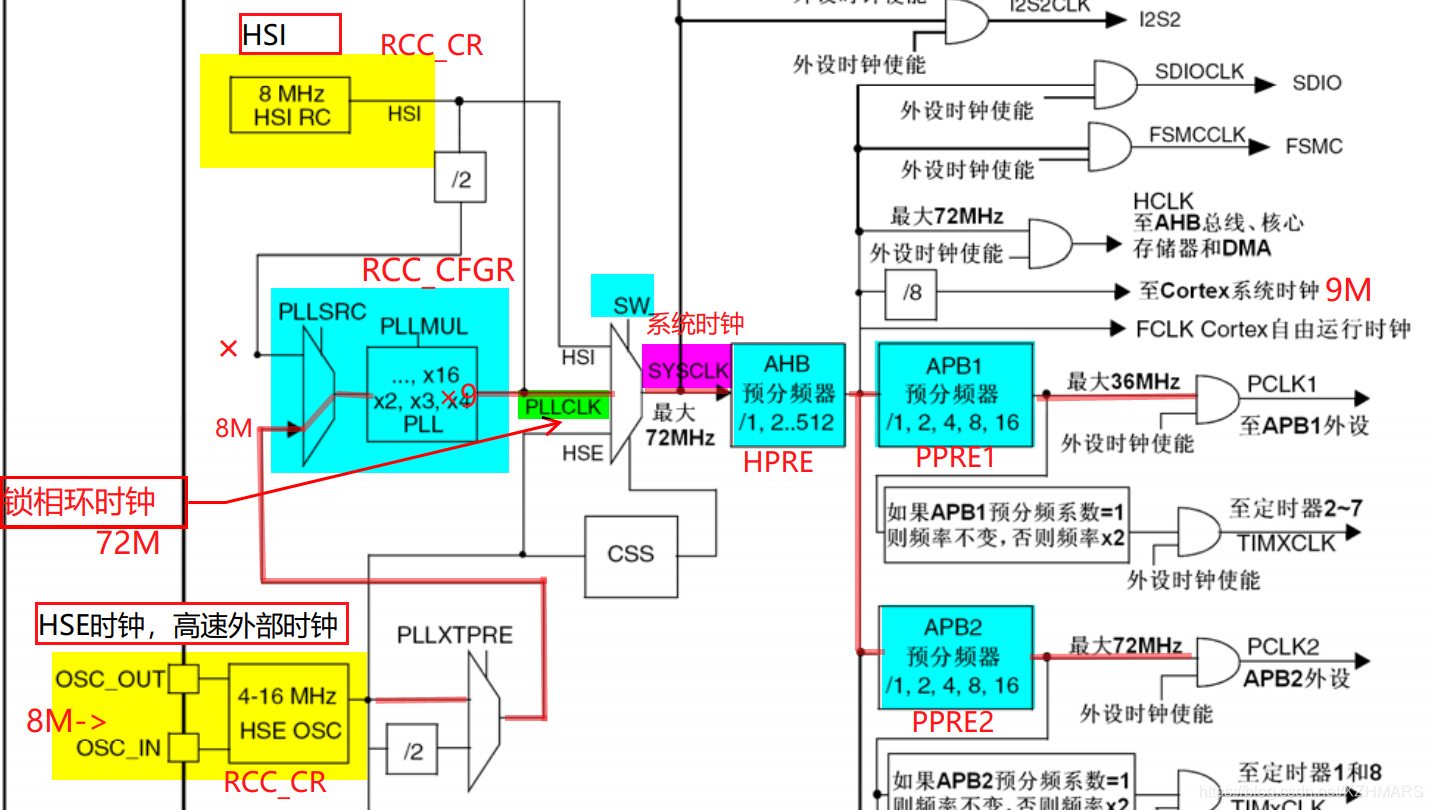

3.合理选择时钟频率

对DDR存储器寻址设计而言,时钟频率的选取显得至关紧要。过高的时钟频率易引发系统稳定性问题;而过低的时钟频率则有碍于系统性能发挥。因此,应根据实际应用环境及硬件配置进行权衡考量后再作抉择。

4.优化布局和引脚分配

DDR地址设计中,谨慎摆位并调配管脚可增进系统效能及稳定性。同时需考虑信号线的适当长度、电源与地线的布放规则,降低信号传输延时及串扰影响。

5.进行严格的信号完整性仿真

DDR地址设计前进行严谨的信号完整性分析至关重要。可通过此方法洞察隐含问题,从而优化调整参数,确保后期调试和修改工作合理开展。

6.使用合适的工具和软件

DDR地址设计运用得当的工具与软件可大幅提升工作效能及精确度。譬如,借助专门的布线设计软体、模拟测试工具以及调试设备等专业辅助手段,有助我们更精准地达成设计目标。

7.不断学习和更新知识

身为DDR寻址设计者,持续学习与更新至关重要。技术日新月异,DDR规范亦随之革新,欲设计更高品质之系统,须以学习为本、紧跟时代步伐。

在此提供我在DDR寻址方面的实践心得与经验分享,以期为同行业者带来有益参考。要设计出高效可靠的DDR寻址系统,需深入了解其规范,充分关注信号完整性,恰当地选取时钟频率,精细调整布局与管脚分配,实施仿真校验,运用适当的工具及软件,并持续保持知识学习与更替。期待各位在DDR寻址设计中大展拳脚,取得优异成果!