DDR3线路堪称计算机主板设计中的难题,身为资深硬件工匠,我在此向您揭示一些行之有效的经验及技巧。下面所列的八大要点,望助广大读者一臂之力。

1.了解信号完整性

在执行DDR3供电线路工程前,必须深入探讨信号完整性理论。其中涵盖信号传播极限速率、电压起伏以及噪音等各种因素对信号品质的影响力。唯有掌握信号完整性知识,方能更高效地完成DDR3供电线路规划与设计。

2.划分信号层

设计DDR3结构时,应将各类信号分置于不同层次以降低干扰提升信号效果。譬如,使用内层用于传输时钟与地址讯号,而外层专门传递数据信息。

3.保持相等长度

为保持数据传输稳定,必须保证各条电缆长度均等。通过调控长度差异可精细调整相位延迟,防止数据传送中出现时序偏差。

4.降低串扰

DR3布线时常遇串扰难题,为有效减轻其危害,可采取差异性信号传输与屏蔽措施相结合。前者能有效弱化信号受干扰程度;后者芬芳外噪对信号产生的不良作用。

5.注意终端匹配

DDR3走线中的终端匹配至关重要,需保证驱动器和终端电阻具备与信号特性阻抗一致的能力,防范反射和衰减等问题发生。

6.考虑布线规则

DDR3布线需遵守特定原则,如规避90°直角转弯,减少线路交汇和平行走向,以降低信号互相干扰程度,从而提升整个系统性能表现。

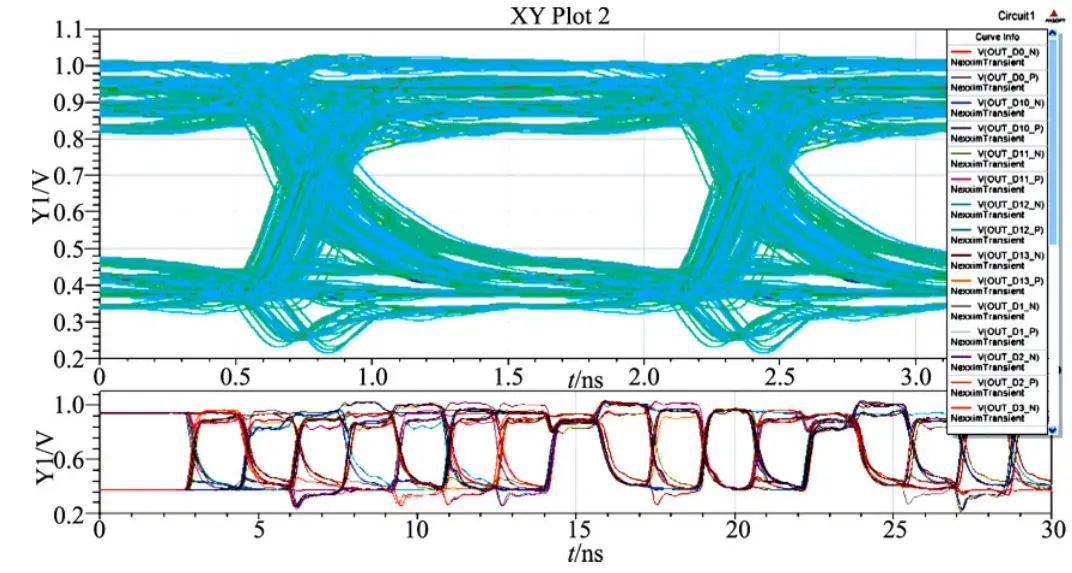

7.进行模拟仿真

在着手DDR3布线设计前,模拟仿真尤为关键。借助仿真工具,我们能洞悉到信号传递全过程所潜在的难题,并适时地对其做必要的调试与改良。

8.反复测试和调整

在完成DDR3布线设计后务必进行多次调试与完善。实际测试有助于暴露潜在缺陷,从而适时加以修正与升级。

总的来说,DDR3走线任务繁复且至关重要。唯有掌控了适当的技艺与丰富的实战经验,方能设计制造出优质高效的计算机主板。期望我的心得体会能够为诸位带来裨益,携手共进、共创辉煌未来!